- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄231491 > W3E232M16S-266STIG (WHITE ELECTRONIC DESIGNS CORP) 64M X 16 DDR DRAM, 0.7 ns, PDSO66 PDF資料下載

參數(shù)資料

| 型號: | W3E232M16S-266STIG |

| 廠商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分類: | DRAM |

| 英文描述: | 64M X 16 DDR DRAM, 0.7 ns, PDSO66 |

| 封裝: | 0.400 X 0.875 INCH, 0.65 MM PITCH, ROHS COMPLIANT, TSOP2-66 |

| 文件頁數(shù): | 21/22頁 |

| 文件大小: | 0K |

| 代理商: | W3E232M16S-266STIG |

W3E232M16S-XSTX

8

White Electronic Designs Corporation (602) 437-1520 www.wedc.com

White Electronic Designs

December 2005

Rev. 1

White Electronic Designs Corp. reserves the right to change products or specications without notice.

PRELIMINARY*

process of precharging.

TABLE 1 – BURST DEFINITION

Burst

Length

Starting Column

Address

Order of Accesses Within a Burst

Type = Sequential

Type = Interleaved

2

A0

0

0-1

1

1-0

4

A1

A0

0

0-1-2-3

0

1

1-2-3-0

1-0-3-2

1

0

2-3-0-1

1

3-0-1-2

3-2-1-0

8

A2

A1

A0

0

0-1-2-3-4-5-6-7

0

1

1-2-3-4-5-6-7-0

1-0-3-2-5-4-7-6

0

1

0

2-3-4-5-6-7-0-1

2-3-0-1-6-7-4-5

0

1

3-4-5-6-7-0-1-2

3-2-1-0-7-6-5-4

1

0

4-5-6-7-0-1-2-3

1

0

1

5-6-7-0-1-2-3-4

5-4-7-6-1-0-3-2

1

0

6-7-0-1-2-3-4-5

6-7-4-5-2-3-0-1

1

7-0-1-2-3-4-5-6

7-6-5-4-3-2-1-0

NOTES:

1. For a burst length of two, A1-Ai select two-data-element block; A0

selects the starting column within the block.

2. For a burst length of four, A2-Ai select four-data-element block; A0-1

select the starting column within the block.

3. For a burst length of eight, A3-Ai select eight-data-element block;

A0-2 select the starting column within the block.

4. Whenever a boundary of the block is reached within a given

sequence above, the following access wraps within the block.

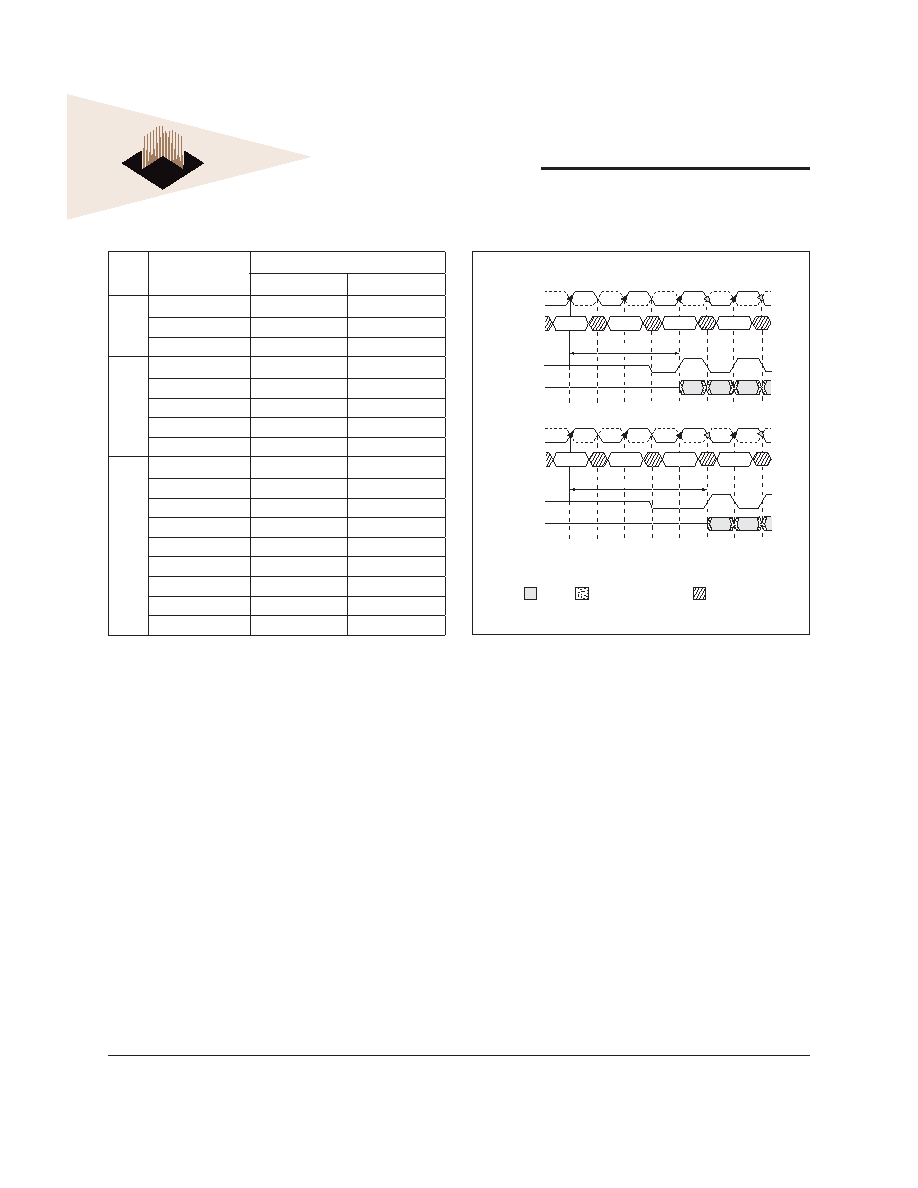

COMMAND

READ

NOP

CL = 2.5

DON'T CARE

TRANSITIONING DATA

DQ

DQS

T0

T1

T2

T2n

T3

T3n

COMMAND

READ

NOP

CL = 2

DQ

DQS

CLK

CLK#

T0

T1

T2

T2n

T3

T3n

Burst Length = 4 in the cases shown

Shown with nominal tAC and nominal tDSDQ

DATA

CLK

CLK#

FIGURE 4 – CAS LATENCY

AUTO PRECHARGE

AUTO PRECHARGE is a feature which performs the

same individual-bank PRECHARGE function described

above, but without requiring an explicit command. This is

accomplished by using A10 to enable AUTO PRECHARGE

in conjunction with a specic READ or WRITE command.

A precharge of the bank/row that is addressed with the

READ or WRITE command is automatically performed

upon completion of the READ or WRITE burst. AUTO

PRECHARGE is nonpersistent in that it is either enabled

or disabled for each individual READ or WRITE command.

The device supports concurrent auto precharge if the

command to the other bank does not interrupt the data

transfer to the current bank.

AUTO PRECHARGE ensures that the precharge is

initiated at the earliest valid stage within a burst. This

“earliest valid stage” is determined as if an explicit

precharge command was issued at the earliest possible

time, without violating tRAS (MIN).The user must not issue

another command to the same bank until the precharge

time (tRP) is completed.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| WPS256K16T-20LJC | 256K X 16 STANDARD SRAM, 20 ns, PDSO44 |

| WMF256K8-70FEM5A | 256K X 8 FLASH 5V PROM, 70 ns, CDFP32 |

| WMS512K8BV-20DEMEA | 512K X 8 STANDARD SRAM, 20 ns, CDSO32 |

| WS512K32-100HQE | 2M X 8 MULTI DEVICE SRAM MODULE, 100 ns, CHMA66 |

| WS512K32-85G2CE | 2M X 8 MULTI DEVICE SRAM MODULE, 85 ns, CQMA68 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W3E232M16S-400STC | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:2x32Mx16bit DDR SDRAM |

| W3E232M16S-400STCG | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:2x32Mx16bit DDR SDRAM |

| W3E232M16S-400STI | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:2x32Mx16bit DDR SDRAM |

| W3E232M16S-400STIG | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:2x32Mx16bit DDR SDRAM |

| W3E232M16S-XSTX | 制造商:WEDC 制造商全稱:White Electronic Designs Corporation 功能描述:2x32Mx16bit DDR SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。