- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359439 > VT83C469 (Electronic Theatre Controls, Inc.) PCMCIA Socket Controller PDF資料下載

參數(shù)資料

| 型號(hào): | VT83C469 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | PCMCIA Socket Controller |

| 中文描述: | PCMCIA插槽控制器 |

| 文件頁(yè)數(shù): | 24/36頁(yè) |

| 文件大?。?/td> | 156K |

| 代理商: | VT83C469 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

VIA Technologies, Inc.

Preliminary

VT83C469

24

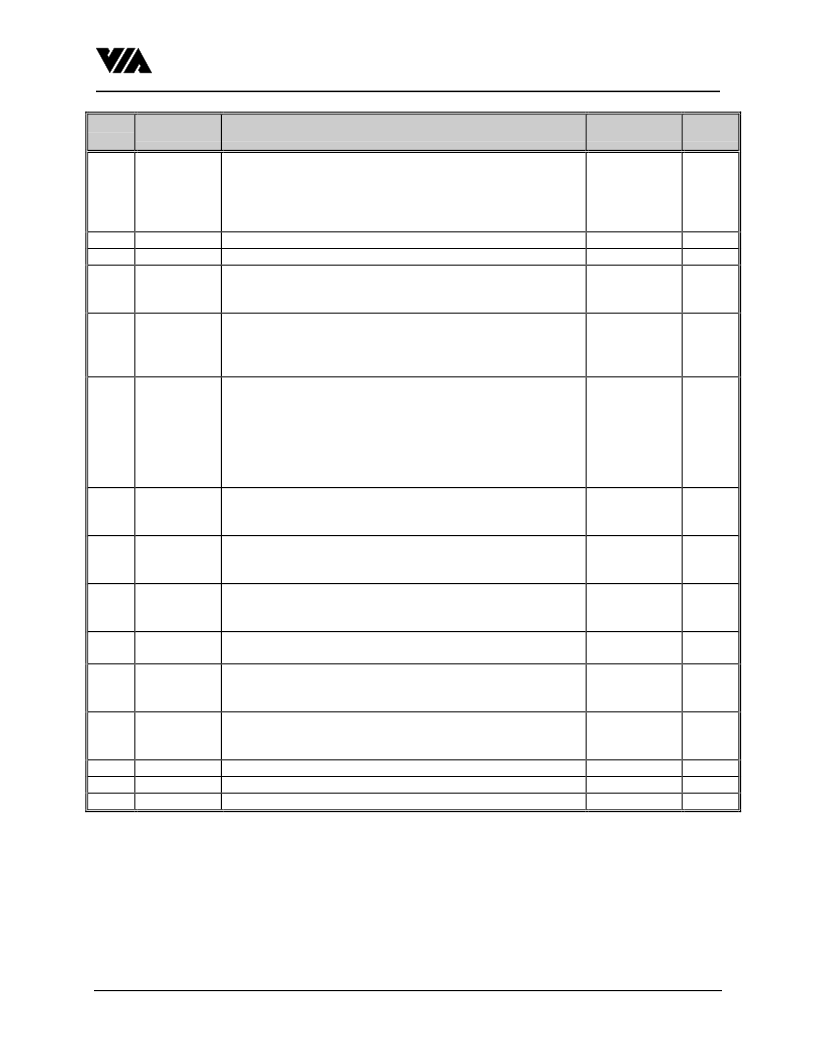

B

US

T

YPE

S

IGNAL

D

ESCRIPTION

P

IN

T

YPE

I

D [15:0]

Card data

2, 4-10, 12, 13,

55-58, 60, 62,

73, 76-82, 84-

85, 126-130,

133

67

68

49, 120

I/O

I

I

S

HDACK#

HTC

INPACK#

HDACK: Host DMA Acknowledge

HTC: Host Terminal Count

Input acknowledge. Asserted by some PC Cards during I/O read

cycles. This signal is used by the VG-468 to control the enable

of its input data buffer between the card and CPU.

Interrupt Request output: Active low output requesting a

nonmaskable interrupt to the CPU. Also, a resistor strapping

input during RESETDRV to determine the mapping of socket A

and socket B to one of four groups.

I/O Channel Ready. This active high signal indicates that the

current I/O bus cycle has been completed. When a PC Card

needs to extend a Read or Write cycle, the VG-468 pulls

IOCHRDY low. IOCHRDY can be deasserted by either WAIT#,

or by programming to add wait states for 16-bit memory and I/O

cycles. If WAIT# is used in 16-bit mode, the wait state generator

has to be set to 1 wait state.

This active low I/O 16-bit chip select signal indicates to the host

system the current I/O cycle is a 16-bit access. A 16-bit to 8-bit

conversion is done if it is inactive.

I/O Read signal is driven active to read data from the PC Card's

I/O space. The REG# signal and at least one of the Card Enable

signals must also be active for the I/O transfer to take place.

I/O Write signal is driven active to write data to the PC Card's

I/O space. The REG# signal and at least one of the Card Enable

signals must also be active for the I/O transfer to take place.

IRQ [15, 14, 12:9, 7, 5:3]

I

I

I

S

INTR#

152

I/O

I

IOCHRDY

150

O

I

IOCS16#

148

O

I

IORD#

20, 91

O

I

IOWR#

22, 93

O

I

IRQs

136-140, 146-

142

181-175

O

I

LA [23:17]

Local Address bus used to address memory devices on the ISA-

bus. Together with the system address signals, they address up to

16MB on the ISA bus.

This active low 16-bit memory chip select signal indicates to the

host system that the current memory cycle is a 16-bit access

cycle. A 16-bit to 8-bit conversion is done if it is inactive.

Active low signal indicated a memory read cycle.

Active low signal indicates a memory write cycle.

Active low signal used to gate memory reads from memory cards.

I

I

MEMCS16#

149

O

I

I

S

MEMR#

MEMW#

OE#

174

174

16, 87

I

I

O

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VT83C572 | PCI TO USB CONTROLLER |

| VT83N1 | |

| VT80N1 | |

| VT80N2 | |

| VT83N2 | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VT83C572 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCI TO USB CONTROLLER |

| VT83CT | 制造商:PERKINELMER 制造商全稱:PerkinElmer Optoelectronics 功能描述:Photoconductive Cells and Analog Optoisolators (Vactrols) |

| VT83D223 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| VT83D263/2 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| VT83E303 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。