- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359432 > VSC9142 (VITESSE SEMICONDUCTOR CORP) SONET/SDH 2.5Gbps Transport Terminating Transceiver PDF資料下載

參數(shù)資料

| 型號: | VSC9142 |

| 廠商: | VITESSE SEMICONDUCTOR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | SONET/SDH 2.5Gbps Transport Terminating Transceiver |

| 中文描述: | MUX/DEMUX, PBGA320 |

| 封裝: | TBGA-320 |

| 文件頁數(shù): | 25/30頁 |

| 文件大?。?/td> | 259K |

| 代理商: | VSC9142 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁第29頁第30頁

G56054-0, Rev 1.0

SONET/SDH 2.5Gbps Transport Terminating Transceiver

VSC9142

.

4.0 Electrical & Mechanical Data

Page 25

.

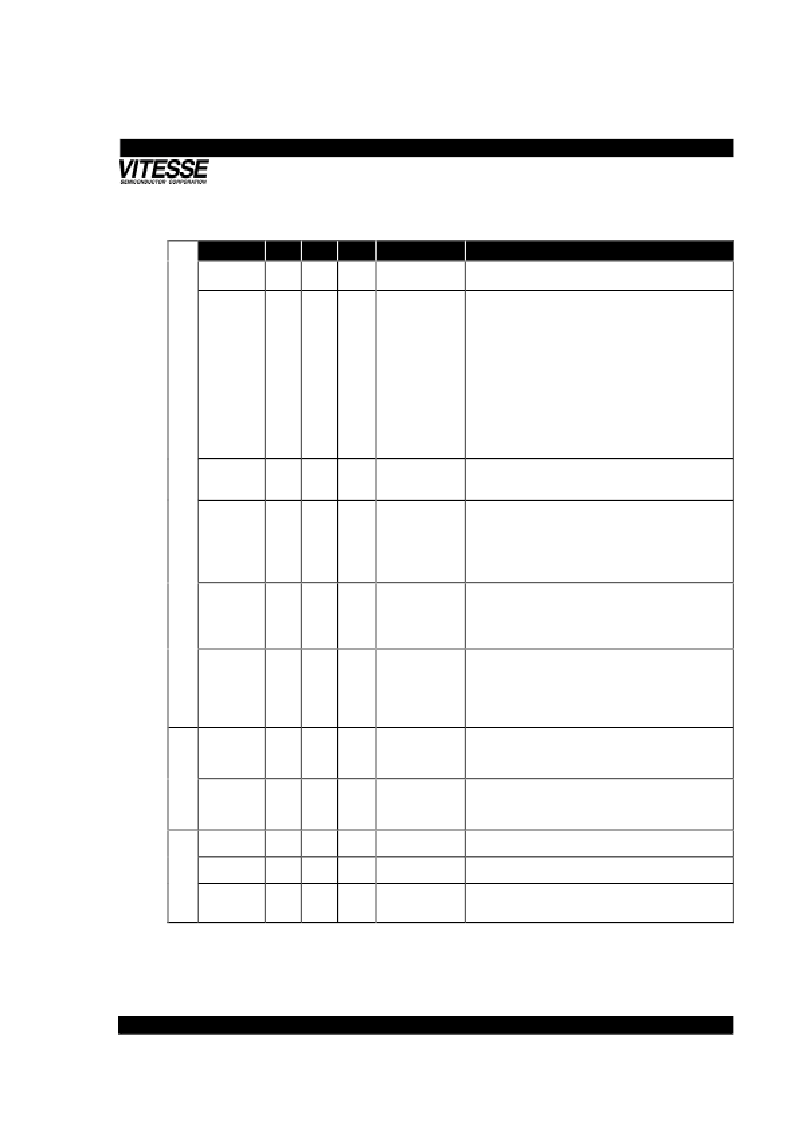

Table 1.1

Hardware Signal Definitions (7 of 12)

Pin Label

POS Mode:

REOP

POS Mode:

RVAL

ATMMode:

RUEMPTY*/

RUCLAV

Pad

AB2

I/O

O

Type

TTL

Signal Name

Receive End of

Packet

Receive Data Valid

or

Receive

Empty/Cell

Available

Description

POS Mode only:

REOP is asserted (active high) to indicate that

RDAT

x

contains the last valid octet of the packet.

POS Mode:

RVAL asserted (active high) indicates that the

recevie data signals (RDAT

x

, RSOP, REOP, RMOD, RPRTY,

and RERR) are valid. When RAL is low, all receive signals are

invalid and must be disregarded. RVAL transitions low when the

Rx FIFO is empty or the end of a packet is reached, and data will

not be removed fromthe Rx FIFO while RVAL is low. Once

deasserted, RVAL remains so until the current PHY has been

deselected.

ATMMode:

RUEMPTY*/RUCLAV indicates

“

Empty

”

or

“

Cell

Available

”

status of the UTOPIA receive interface for flow control.

RUEMPTY*is for word-level flow control; RUCLAV is for cell-

level flow control. Polarity is selectable via an internal register bit

(i.e., RUCLAV active high/RUEMPTY*active low, or vice versa).

POS Mode only:

An asserted RERR flag (active high) indicates

that the packet contained an error (i.e., abort/FCS error). The

RERR flag is only asserted during EOP-marked words.

POS Mode:

RENB is used by the Packet layer to indicate that

the RVAL, RSOP, RPRTY, RDAT

x

, RMOD

x

, REOP, and RERR

signals will be sampled at the end of the nest cycle (active low).

ATMMode:

RUENB*is used by the ATMlayer to indicate that

RUDATA, RUSOC, and RPRTY will be sampled at the end of the

nest cycle (active low).

POS Mode:

RFCLK is a reference clock provided by the Packet

layer to the PHY layer to synchronize transfers on RDAT

x

.

ATMMode:

RUCLK is a reference clock provided by the ATM

layer to the PHY layer to synchronize transfers on RUDATA

x

.

AA2

O

TTL

POS Mode:

RERR

W4

O

TTL

Receive Error

Indicator

POS Mode:

RENB

ATMMode:

RUENB*

AA3

I

TTL

Receive Read

Enable

POS Mode:

RFCLK

ATMMode:

RUCLK

Y4

I

TTL

Receive FIFO

Write Clock

or

Receive Write

Clock

Receive FIFO

Write Clock

Looped

or

Receive Write

Clock Looped

Transmt Time

Stamp

D

POS Mode:

RFCLKO

ATMMode:

RUCLKO

AA4

O

TTL

POS Mode:

RFCLKO is the RFCLK transfer synchronization

reference clock looped out.

ATMMode:

RUCLKO is the RUCLK transfer synchronization

reference clock looped out.

TXTS

AA6

O

TTL

TXTS is an active high pulse generated when a cell/packet exits

the TPP block. The difference in time between a TXTS pulse

and a TSOP/TUSOC pulse can be used to determne transmt

FIFO latency.

RXTS is an active high pulse generated when a new cell/packet

arrives in the RPP block. The difference in time between an

RXTS pulse and an RSOP/RUSOC pulse is used to determne

receive FIFO latency.

This is a status signal for loss of signal (LOS) detection (active

high). LOS status is also indicated by an internal register bit.

This is a status signal for loss of frame (LOF) detection (active

high). LOF status is also indicated by an internal register bit.

This signal is asserted when the cell delineation state machine is

not in SYNC state. This alarmindication is also available via

internal register access.

T

RXTS

AC3

O

TTL

Receive Time

Stamp

LOS

AB5

O

TTL

Loss of Signal

LOF

AA13

O

TTL

Loss of Frame

R

LCD-P

AB4

O

TTL

Loss of Cell

Delineation

相關PDF資料 |

PDF描述 |

|---|---|

| VSC9180 | VSC9180 Arapahoe - 2.5G SONET/SDH Backplane Transceiver |

| VSC9182 | VSC9182 - 40G STS-1 Time Slot Interchange |

| VSC9186 | VSC9186 Killington - Quad STS-48/STM-16 and STS-192/STM-64 Line Interface |

| VSC9187 | VSC9187 Bromley - 3045 x 3045 VT1.5 TSI Switch Fabric |

| VSC9191 | 100 Gbps (40 x 40) SONET/SDH TSI Switch with Dual Rate I/O |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| VSC9180 | 制造商:VITESSE 制造商全稱:Vitesse Semiconductor Corporation 功能描述:VSC9180 Arapahoe - 2.5G SONET/SDH Backplane Transceiver |

| VSC9182 | 制造商:VITESSE 制造商全稱:Vitesse Semiconductor Corporation 功能描述:VSC9182 - 40G STS-1 Time Slot Interchange |

| VSC9186 | 制造商:VITESSE 制造商全稱:Vitesse Semiconductor Corporation 功能描述:VSC9186 Killington - Quad STS-48/STM-16 and STS-192/STM-64 Line Interface |

| VSC9186ZB/D | 制造商:Vitesse Semiconductor Corporation 功能描述:CHIPSET |

| VSC9187 | 制造商:VITESSE 制造商全稱:Vitesse Semiconductor Corporation 功能描述:VSC9187 Bromley - 3045 x 3045 VT1.5 TSI Switch Fabric |

發(fā)布緊急采購,3分鐘左右您將得到回復。