- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359412 > VPX3214C (Electronic Theatre Controls, Inc.) Video Pixel Decoders PDF資料下載

參數(shù)資料

| 型號: | VPX3214C |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Video Pixel Decoders |

| 中文描述: | 視頻解碼器像素 |

| 文件頁數(shù): | 44/80頁 |

| 文件大?。?/td> | 752K |

| 代理商: | VPX3214C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當(dāng)前第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

PRELIMINARY DATA SHEET

VPX 3220 A, VPX 3216 B, VPX 3214 C

MICRONAS INTERMETALL

44

Tristate Cell

Each group of output signals which are tristatable is con-

trolled by a boundary scan cell (output cell type). This al-

lows either the normal system signal or the scanned sig-

nal to control the tristate control. In the VPX, there are

four such tristate control cells which control groups of

output signals (see section “Output Driver Tristate Con-

trol” for further information).

Bidirect Cell

The bidirect cell is comprised of an input cell and a tris-

tate cell as described in the IEEE standard. The signal

PIXCLK is a bidirectional signal.

5.2.4. Bypass Register

This register provides a minimal path between TDI and

TDO. This is required for complicated boards where

many chips may be connected in serial.

5.2.5. Device Identification Register

This is an optional 32-bit register which contains the-

INTERMETALL identification code (JEDEC controlled),

part and revision number. This is useful in providing the

tester with assurance that the correct part and revision

are inserted into a PCB.

5.2.6. Master Mode Data Register

This is an optional register used to control an 8-bit test

register in the chip. This register supports shift and up-

date. No capture is supported. This was done so the last

word can be shifted out for verification.

5.3. Exception to IEEE 1149.1

There is one exception to IEEE 1149.1. The exception

is to paragraphs 3.1.1.c., 3.5.1.b, and 5.2.1.d (TEST-

LOGIC-RESET state). Because of pin limitations on the

chip, a pin is shared for two functions. When the circuit

is in the TEST-LOGIC-RESET state, the ALPHA signal

is driven out the TDO/ALPHA pin. When the circuit

leaves the TEST-LOGIC-RESET state, the TDO signal

is driven on this line. As long as the circuit is not in the

TEST-LOGIC-RESET state, all the rules for application

of the TDO signal adhere to the IEEE1149.1 spec.

Since the VPX uses the JTAG function as a boundary-

scan tool, the VPX does not sacrifice test of this pin since

it is verified by exercising JTAG function. The designer

of the PCB must make careful note of this fact, since he

will not be able to scan into chips receiving the ALPHA

signal via the VPX. The PCB designer may want to put

this chip at the end of the chain or bring the VPX TDO out

separately and not have it feed another chip in a chain.

5.4. IEEE 1149.1-1990 Spec Adherence

This section defines the details of the IEEE1149.1 de-

sign for the VPX. It describes the function as outlined by

IEEE1149.1, section 12.3.1. The section of that docu-

ment is referenced in the description of each function.

5.4.1. Instruction Register

(section 12.3.1.b.i of IEEE 1149.1-1990)

The instruction register is three bits long. No parity bit is

included. The pattern loaded in the instruction register

during CAPTURE-IR is binary “101” (MSB to LSB). The

two LSBs are defined by the spec to be “01” (bit 1 and

bit 0) while the MSB (bit 2) is set to “1”.

5.4.2. Public Instructions

(Section 12.3.1.b.ii of IEEE 1149.1-1990)

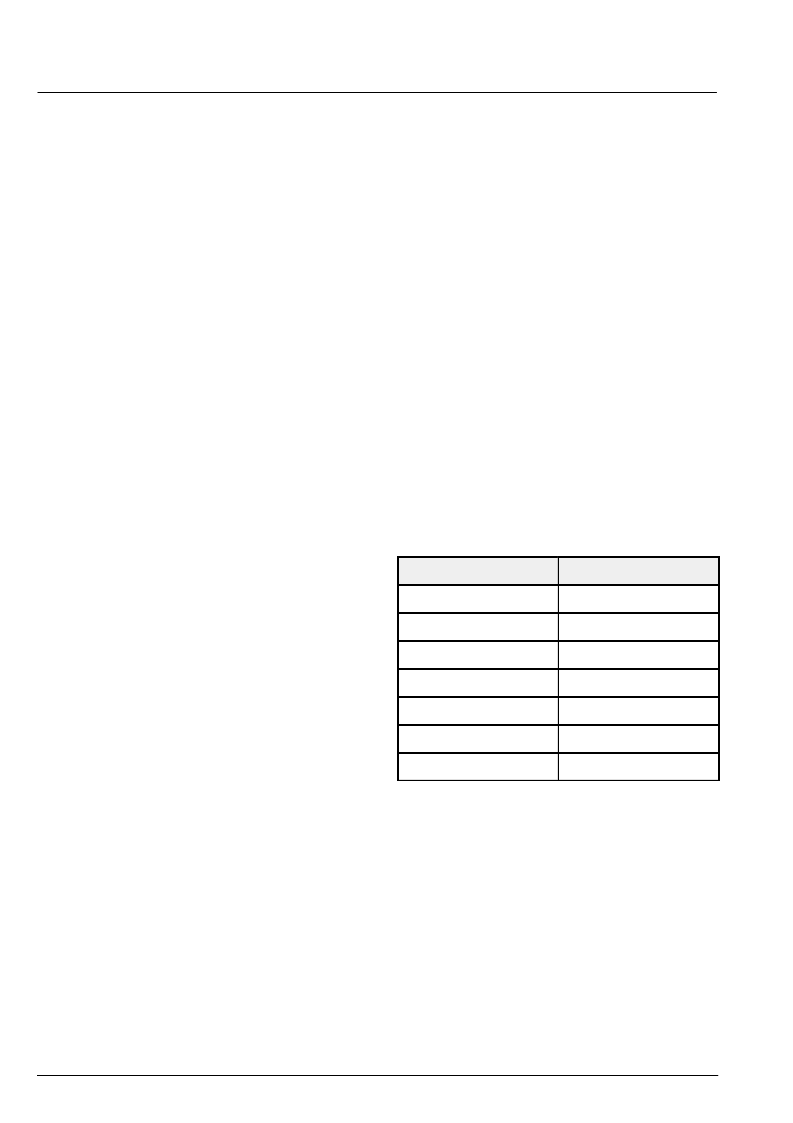

A list of the public instructions is as follows:

Instruction

Code (MSB to LSB)

EXTEST

000

SAMPLE/PRELOAD

001

ID CODE

010

MASTER MODE

011

HIGHZ

100

CLAMP

110

BYPASS

100 – 111

The EXTEST and SAMPLE/PRELOAD instructions

both apply the boundary scan chain to the serial path.

The ID CODE instruction applies the ID register to the

serial chain. The BYPASS, the HIGHZ, and the CLAMP

instructions apply the bypass register to the serial chain.

The MASTER MODE instruction is a test data instruction

for public use. It provides the ability to control an 8-bit

test register in the chip.

5.4.3. Self-test Operation

(Section 12.3.1.b.iii of IEEE 1149.1-1990). There is no

self-test operation included in the VPX design which is

accessible via the TAP.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VPX3224D | Video Pixel Decoders |

| VPX3224E | Video Pixel Decoders |

| VPX322XE | Video Pixel Decoders |

| VQ1000J | N-Channel Enhancement-Mode MOSFET Transistor(最小漏源擊穿電壓60V,夾斷電流0.225A的N溝道增強型MOSFET晶體管) |

| VQ1000J | N-Channel 60-V (D-S) MOSFET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VPX3214C(PLCC44) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Decoder Circuit |

| VPX3214C(QFP44) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Decoder Circuit |

| VPX3216B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video Pixel Decoders |

| VPX3216B(PLCC44) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Decoder Circuit |

| VPX3216B(QFP44) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Decoder Circuit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。