- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383981 > UPD44324184F5-E50-EQ2 (NEC Corp.) 36M-BIT DDRII SRAM 4-WORD BURST OPERAT PDF資料下載

參數(shù)資料

| 型號(hào): | UPD44324184F5-E50-EQ2 |

| 廠商: | NEC Corp. |

| 英文描述: | 36M-BIT DDRII SRAM 4-WORD BURST OPERAT |

| 中文描述: | 36M條位SRAM的4條DDRII詞爆生產(chǎn)營運(yùn) |

| 文件頁數(shù): | 22/32頁 |

| 文件大小: | 315K |

| 代理商: | UPD44324184F5-E50-EQ2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

22

Preliminary Data Sheet

M16781EJ1V0DS

μ

PD44324084, 44324094, 44324184, 44324364

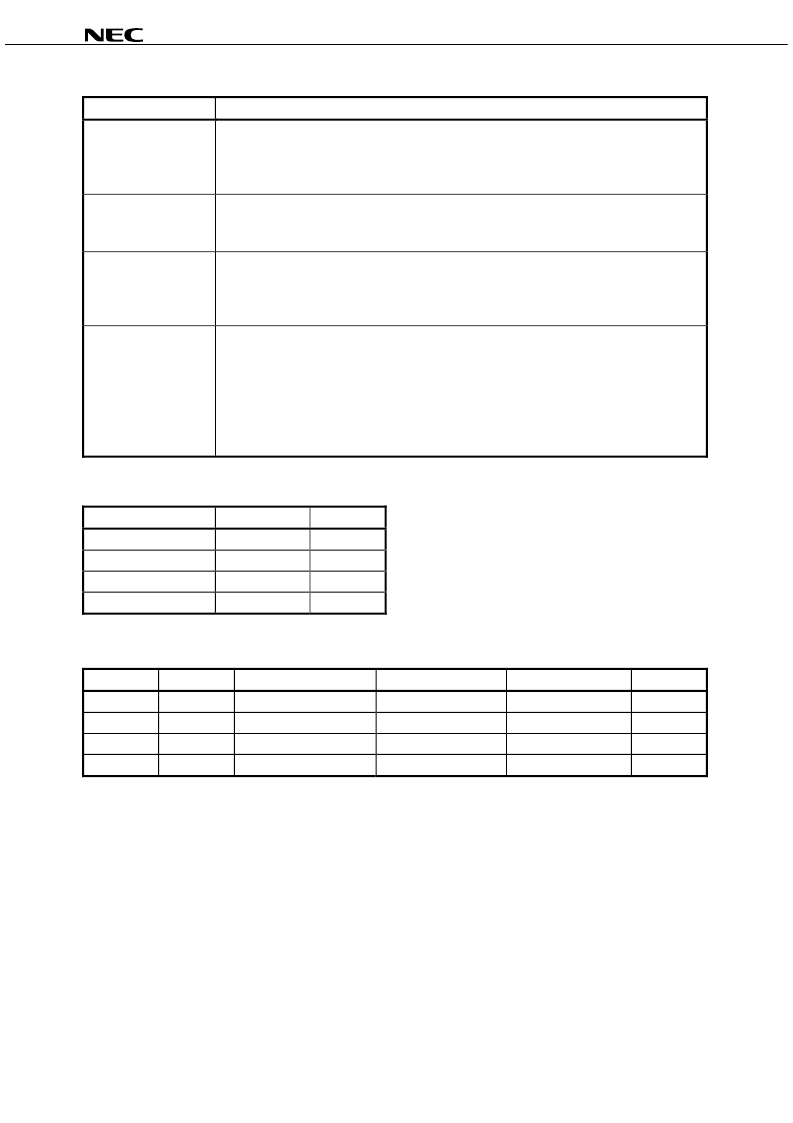

Scan Register Definition (1)

Register name

Description

Instruction register

The instruction register holds the instructions that are executed by the TAP controller when it is

moved into the run-test/idle or the various data register state. The register can be loaded when it is

placed between the TDI and TDO pins. The instruction register is automatically preloaded with the

IDCODE instruction at power-up whenever the controller is placed in test-logic-reset state.

Bypass register

The bypass register is a single bit register that can be placed between TDI and TDO. It allows serial

test data to be passed through the RAMs TAP to another device in the scan chain with as little delay

as possible.

ID register

The ID Register is a 32 bit register that is loaded with a device and vendor specific 32 bit code when

the controller is put in capture-DR state with the IDCODE command loaded in the instruction register.

The register is then placed between the TDI and TDO pins when the controller is moved into shift-DR

state.

Boundary register

The boundary register, under the control of the TAP controller, is loaded with the contents of the

RAMs I/O ring when the controller is in capture-DR state and then is placed between the TDI and

TDO pins when the controller is moved to shift-DR state. Several TAP instructions can be used to

activate the boundary register.

The Scan Exit Order tables describe which device bump connects to each boundary register

location. The first column defines the bit’s position in the boundary register. The second column is

the name of the input or I/O at the bump and the third column is the bump number.

Scan Register Definition (2)

Register name

Bit size

Unit

Instruction register

3

bit

Bypass register

1

bit

ID register

32

bit

Boundary register

109

bit

ID Register Definition

Part number

Organization ID [31:28] vendor revision no.

ID [27:12] part no.

ID [11:1] vendor ID no.

ID [0] fix bit

μ

PD44324084

4M x 8

XXXX

0000 0000 0100 0001

00000010000

1

μ

PD44324094

4M x 9

XXXX

0000 0000 0100 0010

00000010000

1

μ

PD44324184

2M x 18

XXXX

0000 0000 0100 0011

00000010000

1

μ

PD44324364

1M x 36

XXXX

0000 0000 0100 0100

00000010000

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD444004LLE-A10 | 4M-BIT CMOS FAST SRAM 1M-WORD BY 4-BIT |

| UPD444004LLE-A12 | 4M-BIT CMOS FAST SRAM 1M-WORD BY 4-BIT |

| UPD444004LLE-A8 | 4M-BIT CMOS FAST SRAM 1M-WORD BY 4-BIT |

| UPD444004L | 4M-BIT CMOS FAST SRAM 1M-WORD BY 4-BIT |

| UPD444008LLE-A10 | 4M-BIT CMOS FAST SRAM 512K-WORD BY 8-BIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD44324185BF5-E40-FQ1 | 制造商:Renesas Electronics Corporation 功能描述:SRAM Chip Sync Dual 1.8V 36M-Bit 2M x 18 0.45ns 165-Pin BGA 制造商:Renesas Electronics Corporation 功能描述:36MB, DDRII SRAM - Trays 制造商:Renesas Electronics Corporation 功能描述:IC SRAM DDRII 36MBIT 165BGA |

| UPD44324362BF5-E40-FQ1 | 制造商:Renesas Electronics Corporation 功能描述:36MB, DDRII SRAM - Trays 制造商:Renesas Electronics Corporation 功能描述:IC SRAM DDRII 36MBIT 165BGA |

| UPD44324362BF5-E40-FQ1-A | 制造商:Renesas Electronics Corporation 功能描述:36MB, DDRII SRAM - Trays 制造商:Renesas Electronics Corporation 功能描述:IC SRAM DDRII 36MBIT 165BGA |

| UPD44324365BF5-E40-FQ1 | 制造商:Renesas Electronics Corporation 功能描述:36MB, DDRII SRAM - Trays 制造商:Renesas Electronics Corporation 功能描述:IC SRAM DDRII 36MBIT 165BGA |

| UPD44324365BF5-E40-FQ1-A | 制造商:Renesas Electronics Corporation 功能描述:36MB, DDRII SRAM - Trays 制造商:Renesas Electronics Corporation 功能描述:IC SRAM DDRII 36MBIT 165BGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。