- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384039 > UPC1854ACT (NEC Corp.) I2C BUS-COMPATIBLE US MTS PROCESSING LSI PDF資料下載

參數(shù)資料

| 型號: | UPC1854ACT |

| 廠商: | NEC Corp. |

| 英文描述: | I2C BUS-COMPATIBLE US MTS PROCESSING LSI |

| 中文描述: | I2C總線兼容美國的多邊貿(mào)易體制處理LSI |

| 文件頁數(shù): | 41/48頁 |

| 文件大小: | 251K |

| 代理商: | UPC1854ACT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當(dāng)前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

μ

PC1854A

41

Data Sheet S12816EJ3V0DS00

(5/7)

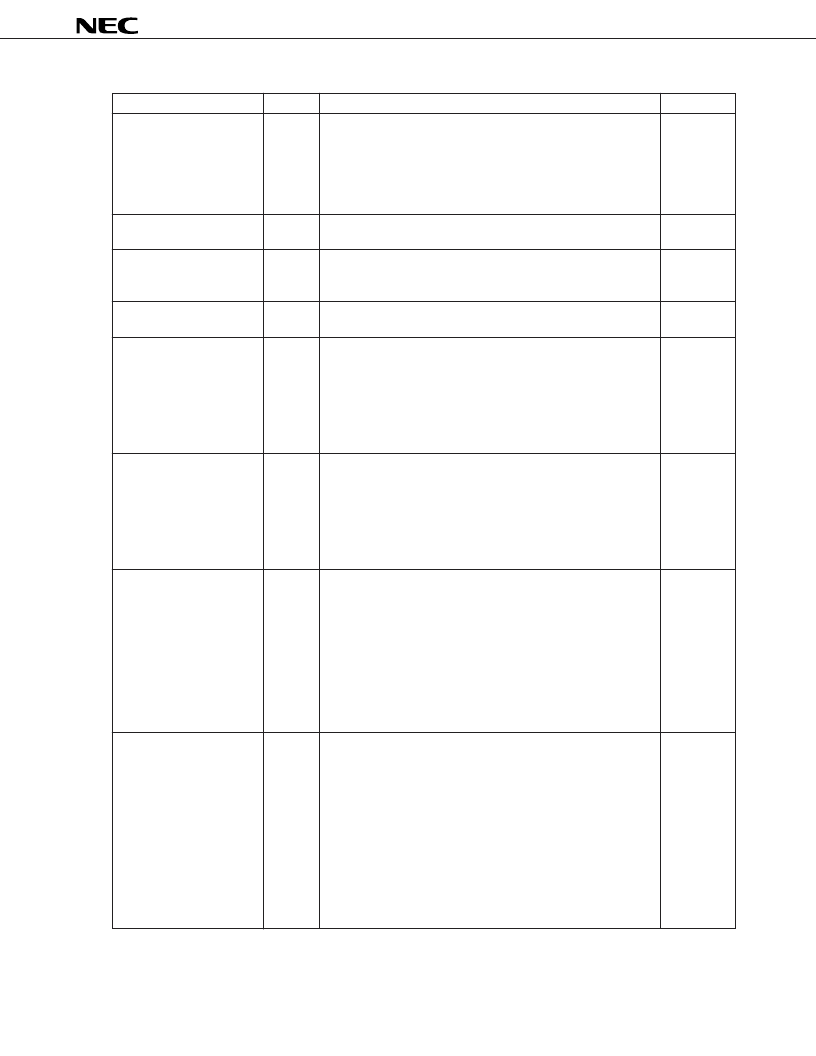

Parameter

Symbol

Test Conditions

User Mode

Note

Stereo total harmonic

distortion 2

THD

ST2

L-channel

THD

ST2

: Distortion rate of LOT pin

COM pin : Stereo signal (L-only, 8 kHz, 30% modulation) input

R-channel

THD

ST2

: Distortion rate of ROT pin

COM pin : Stereo signal (R-only, 8 kHz, 30% modulation) input

Stereo

SAP total harmonic distortion THD

SAP1

THD

SAP1

: Distortion rate of LOT and ROT pins

COM pin : SAP signal (1 kHz, 100% modulation) input

SAP1

SAP single harmonic

distortion

THD

SAP2

THD

SAP2

: Distortion rate of SOT pin

COM pin : SAP signal (1 kHz, 100% modulation,

Noise reduction off) input

SAP

Normal output harmonic

distortion

THD

NO

THD

NO

: Distortion rate of NOT pin

COM pin : Monaural signal (1 kHz, 100% modulation) input

Monaural

Crosstalk 1 (SAP

→

stereo)

CT

1

CT

1

= 20 log (V

CT1

÷

V

L

)

V

CT1

: V

L

after BPF (3 kHz)

V

L

: Output voltage of LOT pin

COM pin : Composite signal {Stereo signal (L-only, 800 Hz, 30%

modulation) and SAP signal (3 kHz, 30 % modulation) }

input

BPF : Attenuation of 0 dB at 3 kHz and 80 dB at 800 Hz, or more

Stereo

Crosstalk 2 (stereo

→

SAP)

CT

2

CT

2

= 20 log (V

CT2

÷

V

L

)

V

CT2

: V

L

after BPF (3 kHz)

V

L

: Output voltage of LOT pin

COM pin : Composite signal {SAPsignal (800 Hz, 30% modulation)

and Stereo signal (L-only, 3 kHz, 30 % modulation) }

input

BPF : Attenuation of 0 dB at 3 kHz and 80 dB at 800 Hz, or more

SAP1

Monaural total S/N

S/N

MO

L-channel

S/N

MO

= 20 log (V

OMOL

÷

V

L

)

V

OMOL

: Output voltage of LOT pin

COM pin : Monaural signal (300 Hz, 100% modulation) input

V

L

: Output voltage of LOT pin (no signal)

R-channel

S/N

MO

= 20 log (V

OMOR

÷

V

R

)

V

OMOR

: Output voltage of ROT pin

COM pin : Monaural signal (300 Hz, 100% modulation) input

V

R

: Output voltage of ROT pin (no signal)

Monaural

Stereo total S/N

S/N

ST

L-channel

S/N

ST

= 20 log (V

OSTL

÷

V

L

)

V

OSTL

: Output voltage of LOT pin

COM pin : Stereo signal (L-only, 300 Hz, 100% modulation) input

V

L

: Output voltage of LOT pin

COM pin : Pilot signal input

R-channel

S/N

ST

= 20 log (V

OSTR

÷

V

R

)

V

OSTR

: Output voltage of ROT pin

COM pin : Stereo signal (R-only, 300 Hz, 100% modulation) input

V

R

: Output voltage of ROT pin

COM pin : Pilot signal input

Stereo

Note

For details about the User Mode, refer to chapter

5. MODE MATRIX

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPC1854A | I2C BUS-COMPATIBLE US MTS PROCESSING LSI |

| UPC1862 | BURST LOCK CLOCK GENERATOR |

| UPC1862GS | BURST LOCK CLOCK GENERATOR |

| UPC1883 | BIPOLAR ANALOG INTEGRATED CIRCUIT |

| UPC1909 | Isolated Flyback Switching Regulator with 9V Output |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPC1854AGT | 制造商:NEC 制造商全稱:NEC 功能描述:I2C BUS-COMPATIBLE US MTS PROCESSING LSI |

| UPC1857 | 制造商:NEC 制造商全稱:NEC 功能描述:SOUND CONTROL IC WITH SURROUND AND I2C BUS |

| UPC1857A | 制造商:NEC 制造商全稱:NEC 功能描述:SOUND CONTROL IC WITH SURROUND AND I2C BUS |

| UPC1857ACT | 制造商:NEC 制造商全稱:NEC 功能描述:SOUND CONTROL IC WITH SURROUND AND I2C BUS |

| UPC1860GS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TV/Video Sync Circuit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。