- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98305 > TVP5040PFP (TEXAS INSTRUMENTS INC) COLOR SIGNAL DECODER, PQFP80 PDF資料下載

參數(shù)資料

| 型號: | TVP5040PFP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 顏色信號轉(zhuǎn)換 |

| 英文描述: | COLOR SIGNAL DECODER, PQFP80 |

| 封裝: | POWER, PLASTIC, TQFP-80 |

| 文件頁數(shù): | 90/101頁 |

| 文件大小: | 464K |

| 代理商: | TVP5040PFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁當(dāng)前第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁

2–73

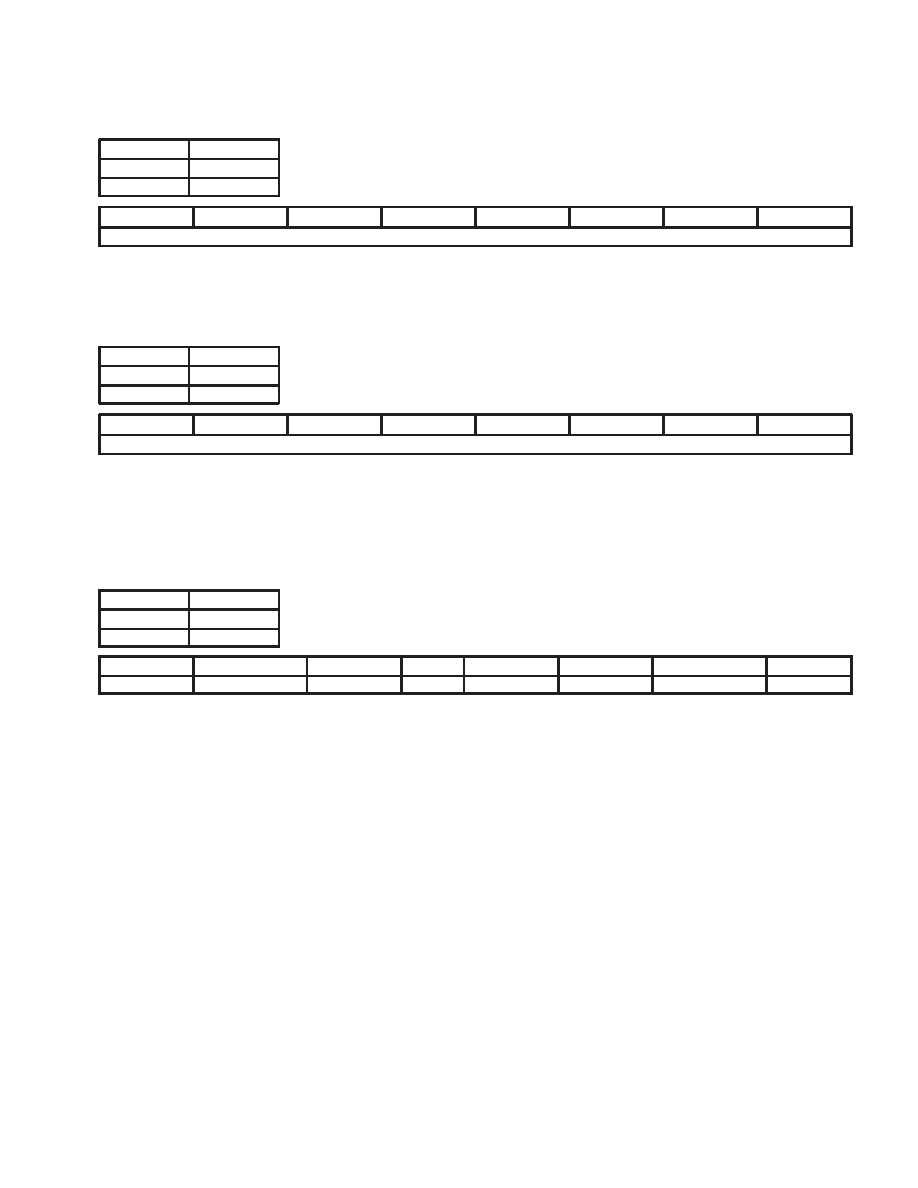

2.13.66 VIP Program RAM Read

VIP address

1600h

PHI address

N/A

I2C address

N/A

7

6

5

4

3

2

1

0

Program RAM Read Data

If the PHI or I2C host interface is enabled, the program RAM can be read via the nonVIP program RAM read register

at address 8E. If the VIP host interface is enabled, the program RAM can be read via VIP FIFO B at location 6 in the

VIP FIFO address space.

2.13.67 Parallel Host Interface Teletext FIFO

VIP address

N/A

PHI address

10

I2C address

N/A

7

6

5

4

3

2

1

0

Teletext FIFO

This read-only register is only accessible when the PHI interface is enabled. To access this register, use the direct

address of 10. Notice almost all the PHI registers are accessed through an indirect address scheme, by writing the

indirect address to address 00 and then write to or read from address 01. This register contains the same information

as the teletext FIFO register at indirect address B0 and is the recommended way of reading data from the teletext

FIFO due to its efficiency.

2.13.68 Parallel Host Interface Status/Interrupt A

VIP address

N/A

PHI address

11

I2C address

N/A

7

6

5

4

3

2

1

0

TvpLOCK state

TvpLOCK interrupt

Cycle complete

Bus error

CC odd field

CC even field

Teletext threshold

Teletext data

The read-write register is only accessible when the VMI interface is enabled. To access this register, use the direct

address of 11. Notice almost all the VMI registers are accessed through an indirect address scheme, by writing the

indirect address to address 00 and then writing to or reading from address 01. This register contains the same

information as the interrupt status register A at indirect address C0 and is the recommended way of reading the

interrupt/status information due to its efficiency. After an interrupt condition is set, it can be reset by writing to this

register with a 1 in the appropriate bit(s).

Teletext Data

*0 = Teletext data buffer empty or we have not reached the video line number that equals

the interrupt line number register

1 = Teletext data buffer contains a complete transaction and the video line number =

interrupt line number

Note this bit can be configured to occur whenever the video line number = interrupt line

number register regardless of the data.

Teletext Threshold

*0 = Threshold not reached

1 = Teletext data in buffer has reached configurable threshold

CC Even Field

*0 = Buffer empty

1 = Even field closed caption buffer contains data

CC Odd Field

*0 = Buffer empty

1 = Odd field closed caption buffer contains data

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TVP5041PFP | COLOR SIGNAL DECODER, PQFP80 |

| TVP5146M1PFP | COLOR SIGNAL DECODER, PQFP80 |

| TVP5146M2IPFPR | COLOR SIGNAL DECODER, PQFP80 |

| TVP5146M2IPFP | COLOR SIGNAL DECODER, PQFP80 |

| TVP5146M2PFPR | COLOR SIGNAL DECODER, PQFP80 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TVP5145 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:NTSC/PAL/SECAM/Component Digital Video Decoder With Macrovision(TM) Detection |

| TVP5145EVM | 制造商:Texas Instruments 功能描述:TVP5145EVM - Bulk |

| TVP5145PFP | 功能描述:視頻 IC NTSC/PAL/SECAM/ Comp Dig Vid Dec RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TVP5146 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:NTSC/PAL / SECAM 4 X 10 BIT DIGITAL VIDEO DECODER WITH MACROVISION DETECTION YPBPR/RGB INPUTS 5 LINE COMB FILTER AND SCART SUPPORT |

| TVP5146_12 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:NTSC/PAL/SECAM 4x10-Bit Digital Video Decoder With Macrovision?£a Detection, YPbPr/RGB Inputs, 5-Line Comb Filter, and SCART Support |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。