- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98305 > TVP5040PFP (TEXAS INSTRUMENTS INC) COLOR SIGNAL DECODER, PQFP80 PDF資料下載

參數(shù)資料

| 型號: | TVP5040PFP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 顏色信號轉(zhuǎn)換 |

| 英文描述: | COLOR SIGNAL DECODER, PQFP80 |

| 封裝: | POWER, PLASTIC, TQFP-80 |

| 文件頁數(shù): | 30/101頁 |

| 文件大?。?/td> | 464K |

| 代理商: | TVP5040PFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁

2–18

9

ACK

8

DATA

9

ACK

1-7

DATA

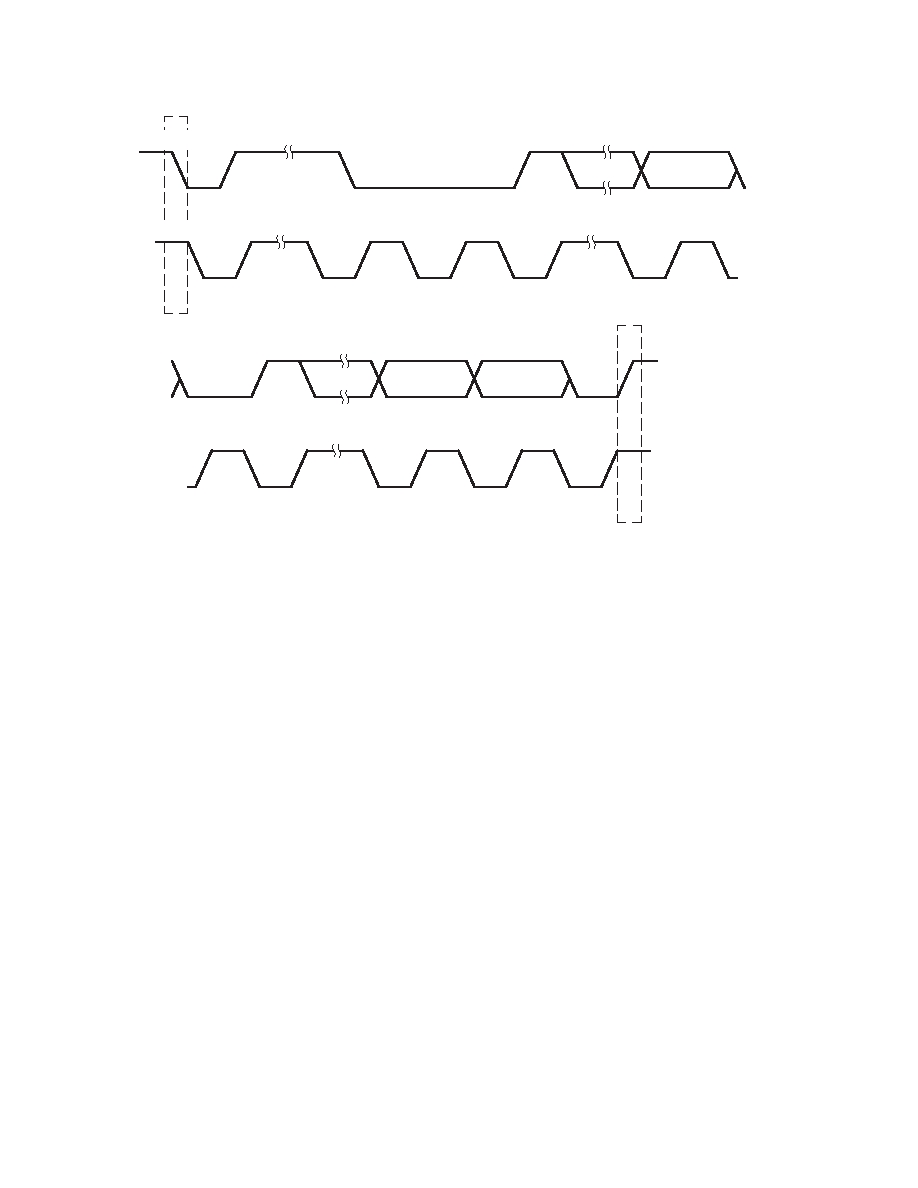

VC0(SCL)

P

Stop Condition

8

DATA

9

ACK

1-7

DATA

8

RW

1-7

ADDRESS

S

Start Condition

VC0(SCL)

VC1(SDA)

Figure 2–27. I2C Data Transfer

The data transfer rate on the bus is up to 400 kbits/s. The number of interfaces connected to the bus is dependent

on the bus capacitance limit of 400 pF. The data on the SDA line must be stable during the high period of the clock.

The high or low state of the data line can only change with the clock signal on the SCL line being low.

If multiple bytes are transferred during one read or write operation, the internal subaddress is automatically

incremented.

A high to low transition on the SDA line while the SCL is high indicates a start condition.

A low to high transition on the SDA line while the SCL is high indicates a stop condition.

Acknowledge (SDA low)

Not-Acknowledge (SDA high)

Every byte placed on the SDA line must be 8-bits long. The number of bytes that can be transferred is unrestricted.

Each byte must be followed by an acknowledge bit. If the slave can not receive another complete byte of data until

it has performed another function, it can hold the clock line (SCL) low to force the master into a wait state. Data transfer

then continues when the slave is ready for another byte of data and releases the clock line (SCL).

The data transfer with acknowledgement is obligatory. The acknowledge related clock pulse is generated by the

master. The master releases the SDA line high during the acknowledge clock pulse. The slave must pull down the

SDA line during the acknowledge clock pulse so that it remains stable low during the high period of this clock pulse.

When a slave does not acknowledge the slave address, the data line must be left high by the slave. The master can

then generate a stop condition to abort the transfer.

If a slave does acknowledge the slave address but some time later in the transfer cannot receive any more data bytes,

the master must again abort the transfer. This is indicated by the slave generating the not acknowledge on the first

byte to follow. The slave leaves the data line high and the master generates the STOP condition.

If a master-receiver is involved in a transfer, it must signal the end of the data to the slave-transmitter by not generating

an acknowledge on the last byte that was clocked out of the slave. The slave-transmitter must release the data line

to allow the master to generate a stop or repeated start condition.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TVP5041PFP | COLOR SIGNAL DECODER, PQFP80 |

| TVP5146M1PFP | COLOR SIGNAL DECODER, PQFP80 |

| TVP5146M2IPFPR | COLOR SIGNAL DECODER, PQFP80 |

| TVP5146M2IPFP | COLOR SIGNAL DECODER, PQFP80 |

| TVP5146M2PFPR | COLOR SIGNAL DECODER, PQFP80 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TVP5145 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:NTSC/PAL/SECAM/Component Digital Video Decoder With Macrovision(TM) Detection |

| TVP5145EVM | 制造商:Texas Instruments 功能描述:TVP5145EVM - Bulk |

| TVP5145PFP | 功能描述:視頻 IC NTSC/PAL/SECAM/ Comp Dig Vid Dec RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TVP5146 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:NTSC/PAL / SECAM 4 X 10 BIT DIGITAL VIDEO DECODER WITH MACROVISION DETECTION YPBPR/RGB INPUTS 5 LINE COMB FILTER AND SCART SUPPORT |

| TVP5146_12 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:NTSC/PAL/SECAM 4x10-Bit Digital Video Decoder With Macrovision?£a Detection, YPbPr/RGB Inputs, 5-Line Comb Filter, and SCART Support |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。