- 您現在的位置:買賣IC網 > PDF目錄384021 > TMS320AV410 (Texas Instruments, Inc.) Digital NTSC/PAL Encoder(數字NTSC/PAL編碼器) PDF資料下載

參數資料

| 型號: | TMS320AV410 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Digital NTSC/PAL Encoder(數字NTSC/PAL編碼器) |

| 中文描述: | 數字的NTSC / PAL編碼器(數字的NTSC / PAL編碼器) |

| 文件頁數: | 6/33頁 |

| 文件大小: | 634K |

| 代理商: | TMS320AV410 |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

TMS320AV410, TMS320AV411

DIGITAL NTSC/PAL ENCODER

SCSS020B – JULY 1996 – REVISED MAY 1997

6

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

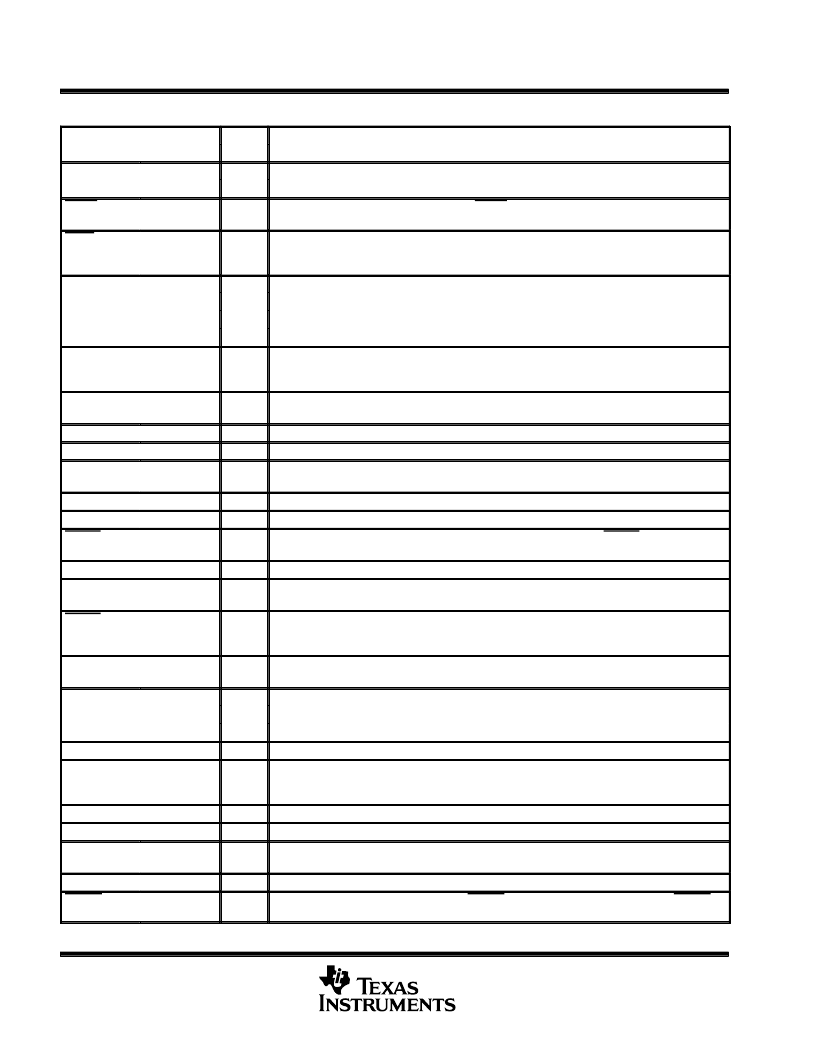

Terminal Functions (Continued)

TERMINAL

I/O

DESCRIPTION

NAME

NO.

66, 65

IMOD0

I

When IFMOD1 is high (stand-alone mode), IMOD1:0 selects the desired format for video input to

h ’AV410 R f

h d

i i

D23 0 i

the ’AV410. Refer to the description for D23:0 pins.

IMOD1

g (

INTER

67

When IFMOD1 is high (stand-alone mode), INTER selects between interlaced and non-interlaced

display. Low selects interlaced mode. High selects non-interlaced mode.

NTSC

52

I

PAL/NTSC mode select

L : NTSC

H : PAL

OL0

57

I

Overlay

h i

d i T bl 1 I I2C

overlay color from the preset color choices listed in Table 1. In I2C or simple serial host interface

mode OL3:0 selects the overlay color from the color choices that have been programmed by the

mode, OL3:0 selects the overlay color from the color choices that have been programmed by the

user in the overlay color registers.

i l h

OL1

58

p

p

OL2

59

OL3

60

OLC

55

I

Overlay switching select

L : Output video signal

H : Output overlay signal

OMOD

69

When IFMOD1 is high (stand-alone mode), OMOD selects the output mode. A low on OMOD

selects, Y, C, composite output. A high selects RGB output.

OSCIN

10

I

External oscillator input or crystal connection

OSCOUT

11

O

Crystal connection (crystal low side)

PHERR

3

O

Phase comparator output. PHERR is input to VCOIN when using the internal PLL to generate the

system clock.

RBIAS0

100

VCO bias resistor 1

RBIAS1

99

VCO bias resistor 2

RESET

7

I

Reset input, active low. A reset action sets all registers to default values. RESET should be toggled

once following device powerup.

SCL

64

I

When IFMOD1 is low (serial host interface modes), SCL is the serial clock input.

In I2C interface mode, SDA is the serial data input/output (open drain). In simple serial interface

mode, SDA is the serial data input.

SDA

65

I/O

SETUP

49

I

In NTSC mode, setup level select:

L : 0% setup

H : 7.5% setup

In simple serial host interface mode, device status is output on SOUT. SOUT is unused in I2C

mode and should be tied low.

SOUT

66

I/O

TEST0

12

I

Device test terminals. Connect to GND for normal operation.

TEST1

72

TEST2

73

TEST3

98

O

PLL test terminal. Should remain floating.

VCC

9, 23, 30, 36,

46, 51, 68, 95,

96

I

3.3-V supply voltage

VCCA

VCCS

VCOIN

77, 78, 97

I

5-V analog supply voltage

16, 61

I

5-V supply voltage

1

I

VCO control voltage input. VCOIN is input from the PHERR terminal when using the internal

PLL to generate the system clock.

VREF

85

I

DAC reference voltage input

VSYNC

15

I/O

Vertical sync pulse. When EXTEN is low, VSYNC is an output. When EXTEN is high, VSYNC is

expected as an input to the device.

P

相關PDF資料 |

PDF描述 |

|---|---|

| TMS320AV411 | Digital NTSC/PAL Encoder(數字NTSC/PAL編碼器) |

| TMS320AV420 | Digital NTSC Encoder(數字NTSC編碼器) |

| TMS320C6424_1 | Fixed-Point Digital Signal Processor |

| TMS320C6455ZTZ | Fixed-Point Digital Signal Processor |

| TMS320C6455ZTZ7 | Fixed-Point Digital Signal Processor |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TMS320AV410PJM | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TMS320AV411 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Encoder Circuit |

| TMS320AV411PJM | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TMS320AV420 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Color Encoder Circuit |

| TMS320AV420PH | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。