- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383954 > TLC320AD535I (Texas Instruments, Inc.) DUAL CHANNEL VOICE/DATA CODEC PDF資料下載

參數(shù)資料

| 型號(hào): | TLC320AD535I |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | Codec |

| 英文描述: | DUAL CHANNEL VOICE/DATA CODEC |

| 中文描述: | 雙通道語(yǔ)音/數(shù)據(jù)編解碼器 |

| 文件頁(yè)數(shù): | 21/84頁(yè) |

| 文件大?。?/td> | 447K |

| 代理商: | TLC320AD535I |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)當(dāng)前第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)

2–6

2.8

Required Minimum Number of MCLK Periods

Master with slave operation is summarized in the following sections.

2.8.1

TLC320AC02 AIC Master-Slave Summary

After initial setup and the master and slave frame syncs are separated, when secondary communication is

needed for a slave device, a 11 must be placed in the 2 LSBs of each primary data word for all devices in

the system, master and slave, by the host processor. In other words, all AICs must receive secondary frame

requests.

The host processor must issue the command by setting D01 and D00 to a 1 in the primary frame sync data

word of all devices. Then the master generates the master primary frame sync and, after the number of shift

clocks set by the FSD register value, the slave primary frame sync intervals. Then, after (B register value/2)

FCLK periods, the master secondary frame sync occurs first, and then the slave secondary frame sync

occurs. These are also rippled through the slave devices.

In other words, when a secondary communications interval is requested by the host processor as described

above:

1.

The master outputs the master primary frame sync interval, and then the slave primary frame

sync intervals after the FSD register value number of shift clocks.

2.

After (B register value/2) FCLK periods, the master then outputs the master secondary frame

sync interval, and after the FSD register value number of shift clocks, the slave secondary frame

sync intervals.

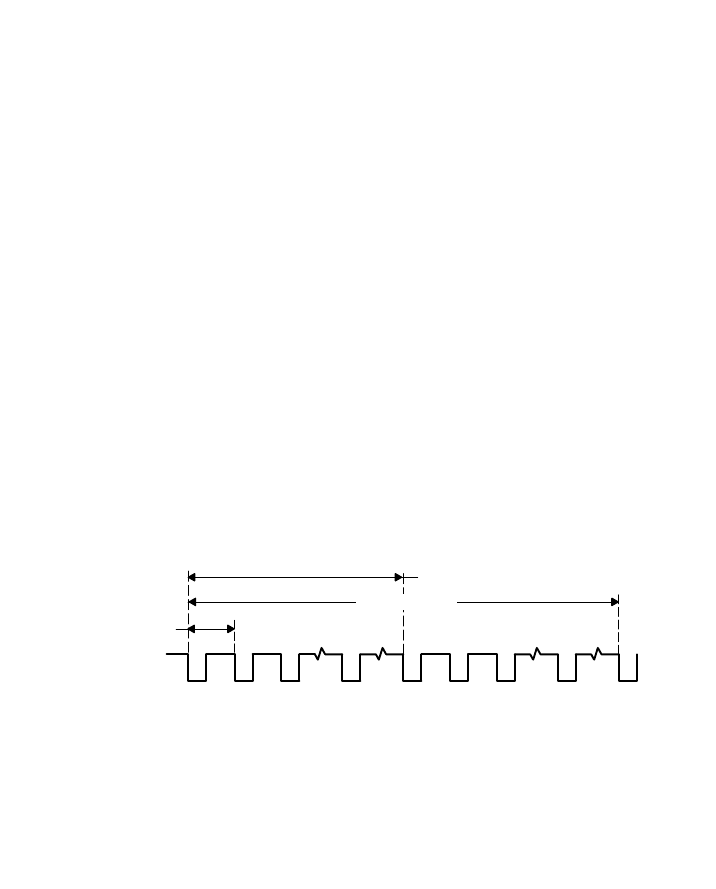

This sequence is shown in Figure 2–2.

The host must keep track of whether the master or a slave is then being addressed and also the number

of slave devices. The master always outputs a 00 in the last 2 bits of the DOUT word, and a slave always

outputs a 1 in the LSB of the DOUT word. This information allows the system to recognize a starting point

by interrogating the least significant bit of the DOUT word. If the LSB is 0, then that device is the master,

and the system is at the starting point.

Note: This identification always happens except in 16-bit mode when the 2 LSBs are not available

for identification purposes.

Sampling Period

(B Register Value/2) FCLK Periods

FSD Value

in SCLKs

Frame Sync

Sequence

MP

SP1

SP2

SPn

MS

SS1

SS2

SSn

MP

Period Symbol

Periods shown: Each period must be a minimum of 16 SCLKs plus 2 additional SCLKs

MP

SP1

SP2

SPn

= Master Primary Period

= 1st Slave Primary Period

= 2nd Slave Primary Period

= nth Slave Primary Period

MS

SS1

SS2

SSn

= Master Secondary Period

= 1st Slave Secondary Period

= 2nd Slave Secondary Period

= nth Slave Secondary Period

Figure 2–2. Timing Sequence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLC320AC02I | Single-Supply Analog Interface Circuit |

| TLC320AD50IPT | SIGMA-DELTA ANALOG INTERFACE CIRCUITS WITH MASTER-SLAVE FUNCTION |

| TLC320AD50(中文) | Sigma-Delta Analog Interface Circuit With Master-Slave Function(Sigma-Delta 模擬接口具主從功能) |

| TLC34075A-110 | Color-Palette(110MHz,視頻接口調(diào)色器) |

| TLC34075A-135 | Color-Palette(135MHz,視頻接口調(diào)色器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLC320AD535IPM | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TLC320AD535PM | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Texas Instruments 功能描述: |

| TLC320AD545-EVM | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TLC320AD545IPT | 功能描述:接口—CODEC Sngl Ch W/Hybrid Op Amps & Speaker Drvr RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLC320AD545IPTG4 | 功能描述:接口—CODEC Sngl Ch W/Hybrid Op Amps & Speaker Drvr RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉(zhuǎn)換速率:48 kSPs 接口類型:I2C ADC 數(shù)量:2 DAC 數(shù)量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。