- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373442 > SN74ALVTH16373DGV (Texas Instruments, Inc.) 2.5-V/3.3-V 16-BIT TRANSPARENT D-TYPE LATCHES WITH 3-STATE OUTPUTS PDF資料下載

參數(shù)資料

| 型號(hào): | SN74ALVTH16373DGV |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 通用總線功能 |

| 英文描述: | 2.5-V/3.3-V 16-BIT TRANSPARENT D-TYPE LATCHES WITH 3-STATE OUTPUTS |

| 中文描述: | 2.5-V/3.3-V 16位透明D型鎖存器具有三態(tài)輸出 |

| 文件頁(yè)數(shù): | 2/10頁(yè) |

| 文件大小: | 185K |

| 代理商: | SN74ALVTH16373DGV |

SN54ALVTH16373, SN74ALVTH16373

2.5-V/3.3-V 16-BIT TRANSPARENT D-TYPE LATCHES

WITH 3-STATE OUTPUTS

SCES067F – JUNE 1996 – REVISED JANUARY 1999

2

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

description (continued)

A buffered output-enable (OE) input can be used to place the eight outputs in either a normal logic state (high

or low logic levels) or a high-impedance state. In the high-impedance state, the outputs neither load nor drive

the bus lines significantly. The high-impedance state and the increased drive provide the capability to drive bus

lines without interface or pullup components.

OE does not affect internal operations of the latch. Old data can be retained or new data can be entered while

the outputs are in the high-impedance state.

Active bus-hold circuitry is provided to hold unused or floating data inputs at a valid logic level.

When V

CC

is between 0 and 1.2 V, the device is in the high-impedance state during power up or power down.

However, to ensure the high-impedance state above 1.2 V, OE should be tied to V

CC

through a pullup resistor;

the minimum value of the resistor is determined by the current-sinking capability of the driver.

The SN54ALVTH16373 is characterized for operation over the full military temperature range of –55

°

C to

125

°

C. The SN74ALVTH16373 is characterized for operation from –40

°

C to 85

°

C.

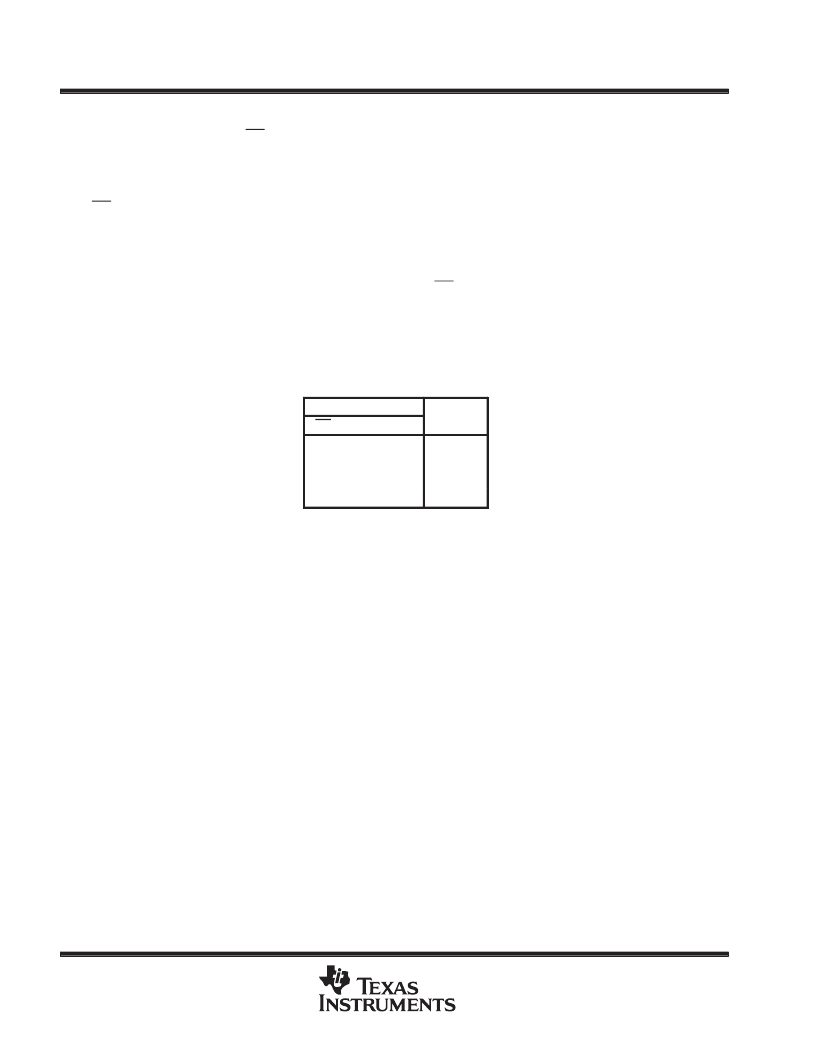

FUNCTION TABLE

(each 8-bit section)

INPUTS

OUTPUT

Q

OE

L

LE

D

H

H

H

L

H

L

L

L

L

X

Q0

Z

H

X

X

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN54ALVTH16373 | 2.5-V/3.3-V 16-Bit D-Latches With 3-State Outputs(2.5V/3.3V 16位D鎖存器(三態(tài)輸出)) |

| SN54ALVTH16374WD | 800mA, 5.0V Output, Low Dropout Voltage Regulator; Package: SOIC-8 Narrow Body; No of Pins: 8; Container: Rail; Qty per Container: 98 |

| SN54ALVTH16374 | 2.5-V/3.3-V 16-Bit Edge-Triggered D-Type Flip-Flops With 3-State Outputs(2.5V/3.3V 16位邊沿D觸發(fā)器(三態(tài)輸出)) |

| SN54ALVTH16500 | 2.5-V/3.3-V 18-Bit Universal Bus Transceivers With 3-State Outputs( 2.5V/3.3V 18位通用總線收發(fā)器(三態(tài)輸出)) |

| SN74ALVTH16500 | 2.5-V/3.3-V 18-Bit Universal Bus Transceivers With 3-State Outputs( 2.5V/3.3V18位通用總線收發(fā)器(三態(tài)輸出)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74ALVTH16373DL | 功能描述:閉鎖 16bit 2.5/3.3V RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時(shí)間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| SN74ALVTH16373DLR | 功能描述:閉鎖 Tri-St 16bit D-Type RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時(shí)間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| SN74ALVTH16373GR | 功能描述:閉鎖 Tri-St 16bit D-Type RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時(shí)間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| SN74ALVTH16373KR | 功能描述:閉鎖 Tri-St 16bit D-Type RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時(shí)間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| SN74ALVTH16373VR | 功能描述:閉鎖 Tri-St 16bit D-Type RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時(shí)間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。