- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄373330 > RTL8150 RTL8150L(M) Specifications PDF資料下載

參數(shù)資料

| 型號(hào): | RTL8150 |

| 英文描述: | RTL8150L(M) Specifications |

| 中文描述: | RTL8150L(米)規(guī)格 |

| 文件頁(yè)數(shù): | 31/58頁(yè) |

| 文件大小: | 616K |

| 代理商: | RTL8150 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)當(dāng)前第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)

RTL8100B(L)

2001-11-9

Rev.1.41

31

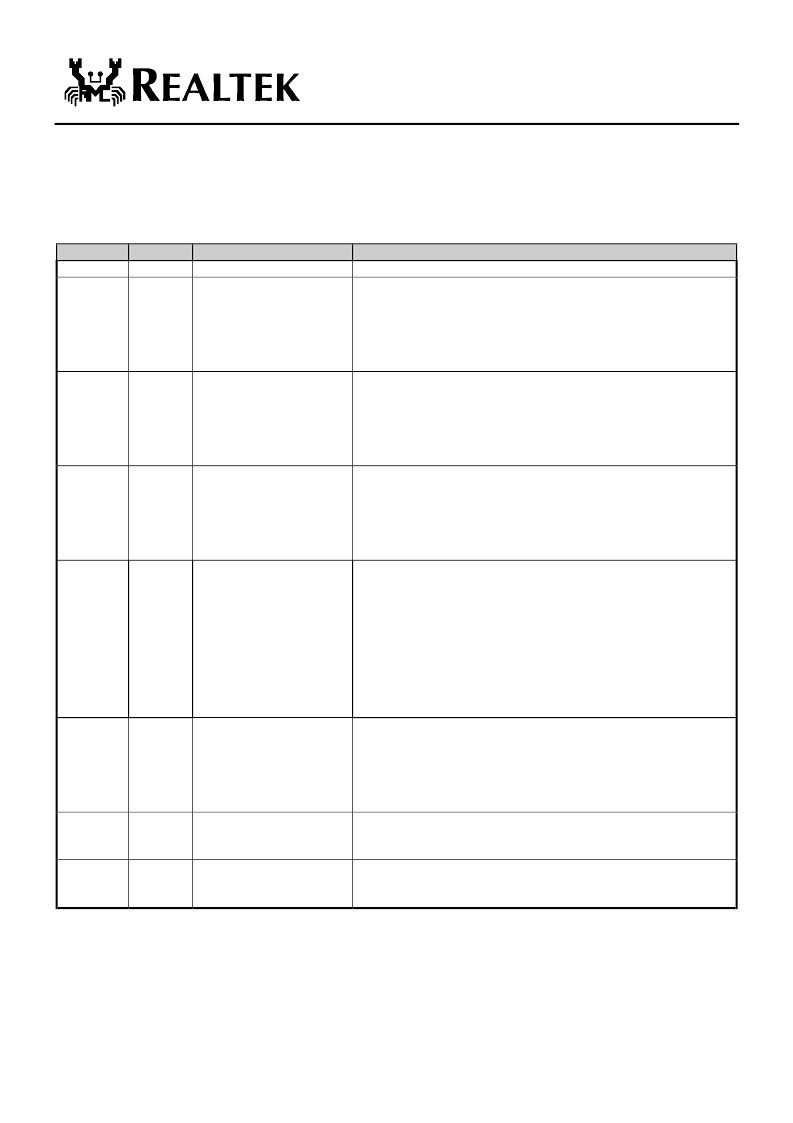

5.28 Config5: Configuration Register 5

(Offset 00D8h, R/W)

This register, unlike other Config registers, is not protected by 93C46 Command register. I.e. there is no need to enable Config

register write prior to writing to Config5.

Bit

7

6

R/W

-

R/W

Symbol

-

BWF

Description

Reserved

Broadcast Wakeup Frame:

1: Enable Broadcast Wakeup Frame with mask bytes of only DID

field = FF FF FF FF FF FF.

0: Default value. Disable Broadcast Wakeup Frame with mask bytes

of only DID field = FF FF FF FF FF FF.

The power-on default value of this bit is 0.

Multicast Wakeup Frame:

1: Enable Multicast Wakeup Frame with mask bytes of only DID

field, which is a multicast address.

0: Default value. Disable Multicast Wakeup Frame with mask bytes

of only DID field, which is a multicast address.

The power-on default value of this bit is 0.

Unicast Wakeup Frame:

1: Enable Unicast Wakeup Frame with mask bytes of only DID field,

which is its own physical address.

0: Default value. Disable Unicast Wakeup Frame with mask bytes of

only DID field, which is its own physical address.

The power-on default value of this bit is 0.

FIFO Address Pointer:

(Realtek internal use only to test FIFO SRAM)

1: Both Rx and Tx FIFO address pointers are updated in descending

way from 1FFh and downwards. The initial FIFO address pointer is

1FFh.

0: (Power-on) default value. Both Rx and Tx FIFO address pointers

are updated in ascending way from 0 and upwards. The initial FIFO

address pointer is 0.

Note: This bit does not participate in EEPROM auto-load. The FIFO

address pointers can not be reset, except initial power-on.

The power-on default value of this bit is 0.

Link Down Power Saving mode:

1: Disable.

0: Enable. When cable is disconnected(Link Down), the analog part

will power down itself (PHY Tx part & part of twister) automatically

except PHY Rx part and part of twister to monitor SD signal in case

that cable is re-connected and Link should be established again.

LANWake signal enable/disable:

1: Enable LANWake signal.

0: Disable LANWake signal.

PME_Status bit:

Always sticky/can be reset by PCI RST# and software.

1: The PME_Status bit can be reset by PCI reset or by software.

0: The PME_Status bit can only be reset by software.

5

R/W

MWF

4

R/W

UWF

3

R/W

FIFOAddrPtr

2

R/W

LDPS

1

R/W

LANWake

0

R/W

PME_STS

Config5 register, offset D8h: (SYM_ERR register is changed to Config5, the function of SYM_ERR register is no longer

supported by RTL8100B(L).)

The 3 bits (bit2-0) are auto-loaded from EEPROM Config5 byte to RTL8100B(L) Config5 register.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RTL8169 | RTL8169 Specification |

| RTL8201L | Layout guide |

| RTL8204 | Layout reference |

| RTL8305SB | RTL8305SB |

| RTL8316 | Specifications |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RTL8168 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:INTEGRATED GIGABIT ETHERNET CONTROLLER FOR PCI EXPRESS TM |

| RTL8169 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:RTL8169 Specification |

| RTL8181 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Wireless LAN Access Point/Gateway Controller |

| RTL8187L | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Wireless LAN network interface controller |

| RTL8187L-LF | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Wireless LAN network interface controller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。