- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372063 > RJ80530NZ001256 Microprocessor PDF資料下載

參數(shù)資料

| 型號: | RJ80530NZ001256 |

| 元件分類: | 微處理器 |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁數(shù): | 5/89頁 |

| 文件大?。?/td> | 1672K |

| 代理商: | RJ80530NZ001256 |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

Mobile Intel

Pentium

III Processor-M Datasheet

298340-002

Datasheet

5

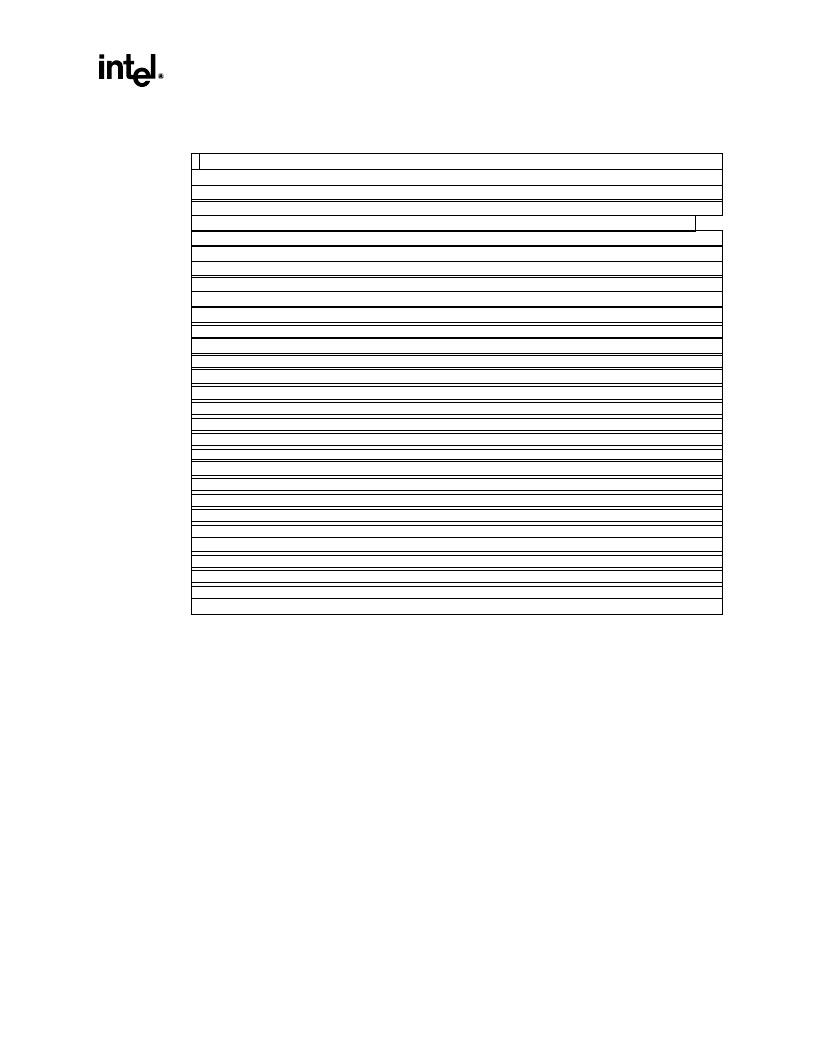

Figures

Figure 1. Clock Control States ..........................................................................................15

Figure 2. PLL RLC Filter....................................................................................................23

Figure 3. VTTPWRGD System-Level Connections...........................................................24

Figure 4. Illustration of V

CC

Static and Transient Tolerances (VID = 1.40V)....................29

Figure 5. Illustration of Deep Sleep V

CC

Static and Transient Tolerances (VID setting

= 1.40V) .............................................................................................................30

Figure 6. BCLK (Single Ended)/PICCLK/TCK Generic Clock Timing Waveform .............41

Figure 7. Differential BCLK/BCLK# Waveform (Common Mode) .....................................41

Figure 8. BCLK/BCLK# Waveform (Differential Mode).....................................................42

Figure 9. Valid Delay Timings ...........................................................................................42

Figure 10.

Setup and Hold Timings...................................................................................43

Figure 11. Cold/Warm Reset and Configuration Timings..................................................43

Figure 12.

Power-on Sequence and Reset Timings..........................................................44

Figure 13. Power Down Sequencing and Timings (VCC Leading)...................................45

Figure 14.

Power Down Sequencing and Timings (V

CCT

Leading) ....................................46

Figure 15.

Test Timings (Boundary Scan) .........................................................................47

Figure 16.

Test Reset Timings...........................................................................................47

Figure 17.

Quick Start/Deep Sleep Timing (BCLK Stopping Method) ...............................48

Figure 18.

Quick Start/Deep Sleep Timing (DPSLP# Assertion Method)..........................48

Figure 19. Enhanced Intel SpeedStep Technology/Deep Sleep Timing...........................49

Figure 20.

BCLK (Single Ended)/PICCLK Generic Clock Waveform ................................51

Figure 21.

Maximum Acceptable Overshoot/Undershoot Waveform.................................52

Figure 22.

Socketable Micro-FCPGA Package - Top and Bottom Isometric Views ..........56

Figure 23.

Socketable Micro-FCPGA Package - Top and Side View................................57

Figure 24. Socketable Micro-FCPGA Package - Bottom View .........................................58

Figure 25.

Micro-FCBGA Package – Top and Bottom Isometric Views ............................60

Figure 26.

Micro-FCBGA Package – Top and Side Views ................................................61

Figure 27.

Micro-FCBGA Package - Bottom View.............................................................62

Figure 28. Pin/Ball Map - Top View...................................................................................63

Figure 29. PLL Filter Specifications ..................................................................................88

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RJ80530VY700256 | Microprocessor |

| RJ80530VZ733256 | Microprocessor |

| RHFL4913 | THREE-TERMINAL POSITIVE FIXED VOLTAGE REGULATORS |

| RHFL4913S50-04V | THREE-TERMINAL POSITIVE FIXED VOLTAGE REGULATORS |

| RHFL4913ESY5005V | Converta Box Enclosure; Enclosure Material:Aluminum; External Height:2"; External Width:8"; External Depth:4"; Enclosure Color:Natural |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RJ80530UY750512 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| RJ80530UZ800512 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| RJ80530UZ933512 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| RJ80530UZ933512S L6CW | 制造商:Intel 功能描述:32-Bit Microprocessor |

| RJ80530VY400256S L6SE | 功能描述:IC CELERON 400MHZ 1.1V UFC-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點:- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。