- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359677 > MT90883IG (Zarlink Semiconductor Inc.) TDM to Packet Processors PDF資料下載

參數(shù)資料

| 型號(hào): | MT90883IG |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | TDM to Packet Processors |

| 中文描述: | TDM到分組處理器 |

| 文件頁數(shù): | 34/97頁 |

| 文件大小: | 702K |

| 代理商: | MT90883IG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當(dāng)前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁

MT90880/1/2/3

Data Sheet

34

Zarlink Semiconductor Inc.

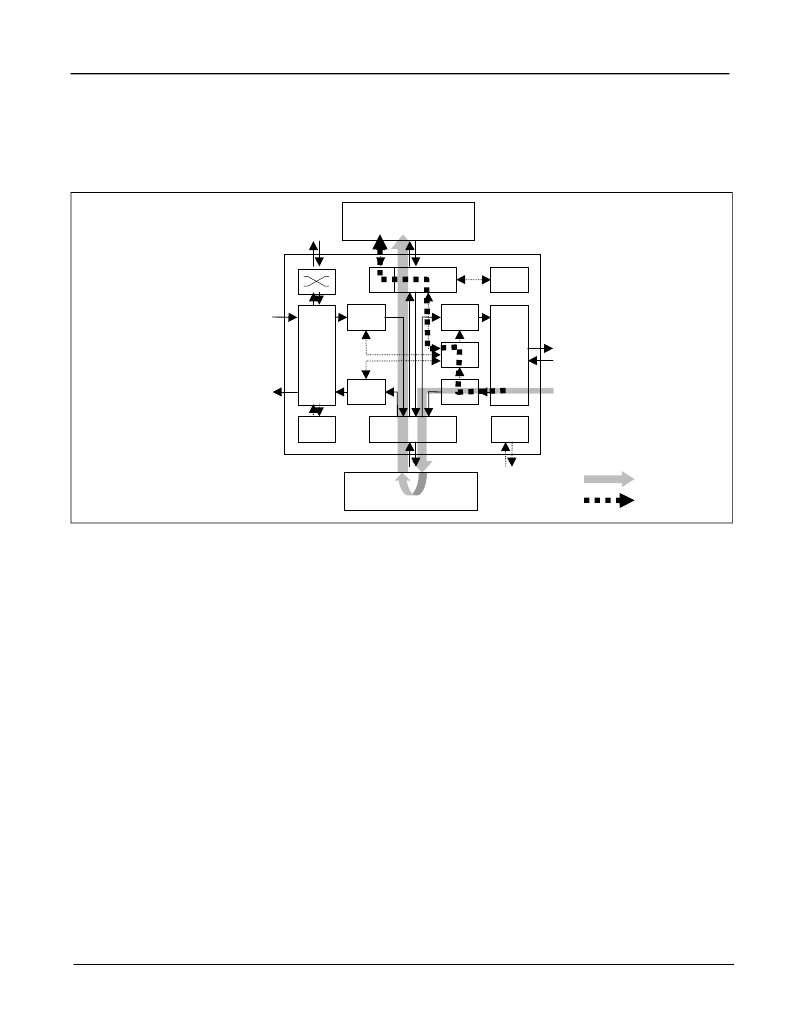

Packet Interface to PCI Interface

Similarly, packets destined for the host CPU or other PCI devices can be sent over the packet network to the

PCI device. The headers of incoming packets are parsed by the Packet Classifier, and can be directed to one of

four queues pointing towards the PCI interface. The classifier can be set-up so that each queue is dedicated to

a specific device or application flow.

Figure 16 - Packet to PCI Data Flow

5.4 Packet Assembly

The incoming TDM data streams are assembled into packet payloads by the WAN Receive block. This can handle

up to 128 active contexts at a time, where each context represents a “virtual channel connection” in CES terms.

Each context generates a single stream of packets, identified by a label in the packet header known as the "context

ID".

A context may contain any number of 64 Kbs channels. These channels need not be contiguous, and in

synchronous mode they can be selected from any input stream. In asynchronous mode each stream is

independently clocked, which can result in phase and frequency differences between streams. Therefore, in this

mode contexts may only contain channels from a single stream.

Channels may be added or deleted dynamically from a context. This feature can be used to optimize bandwidth

utilization. Modifications to the context are synchronized with the start of a new packet.

5.4.1 Payload Order

Packets are assembled sequentially, with each channel placed into the packet as it arrives at the WAN Access

Interface. A fixed order of streams and channels is maintained (see Figure 17), with channel 0, stream 0 placed

before channel 0, stream 1, which is placed before channel 1, stream 0. It is this order that allows the packet to be

correctly disassembled at the far end.

Data Flow

Control Flow

W

P

Packet Memory

Host Processor

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9088IG | TDM to Packet Processors |

| MT8960 | Integrated PCM Filter Codec |

| MT8963AE1 | Integrated PCM Filter Codec |

| MAQ2901CL | Circular Connector; No. of Contacts:85; Series:; Body Material:Aluminum Alloy; Connecting Termination:Solder; Connector Shell Size:40; Circular Contact Gender:Socket; Circular Shell Style:Wall Mount Receptacle RoHS Compliant: No |

| MAQ2901CS | Circular Connector; No. of Contacts:1; Series:; Body Material:Aluminum Alloy; Connecting Termination:Solder; Connector Shell Size:10S; Circular Contact Gender:Pin; Circular Shell Style:Wall Mount Receptacle; Insert Arrangement:10S-2 RoHS Compliant: No |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9088IG | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:TDM to Packet Processors |

| MT9092 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:ISO2-CMOS ST-BUS⑩ FAMILY Digital Telephone with HDLC (HPhone-II) |

| MT9092AP | 制造商:Microsemi Corporation 功能描述: |

| MT9092AP1 | 制造商:Zarlink Semiconductor Inc 功能描述:DGTL TEL 44PLCC - Rail/Tube 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE H-PHONE-PLUS PLCC |

| MT9092APR | 制造商:Microsemi Corporation 功能描述:DGTL TEL 44PLCC - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。