- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384756 > MT48LC8M16A2TG-7E (Micron Technology, Inc.) SYNCHRONOUS DRAM PDF資料下載

參數(shù)資料

| 型號(hào): | MT48LC8M16A2TG-7E |

| 廠商: | Micron Technology, Inc. |

| 英文描述: | SYNCHRONOUS DRAM |

| 中文描述: | 同步DRAM |

| 文件頁(yè)數(shù): | 37/59頁(yè) |

| 文件大?。?/td> | 1822K |

| 代理商: | MT48LC8M16A2TG-7E |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)當(dāng)前第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)

37

128Mb: x4, x8, x16 SDRAM

128MSDRAM_E.p65

–

Rev. E; Pub. 1/02

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2001, Micron Technology, Inc.

128Mb: x4, x8, x16

SDRAM

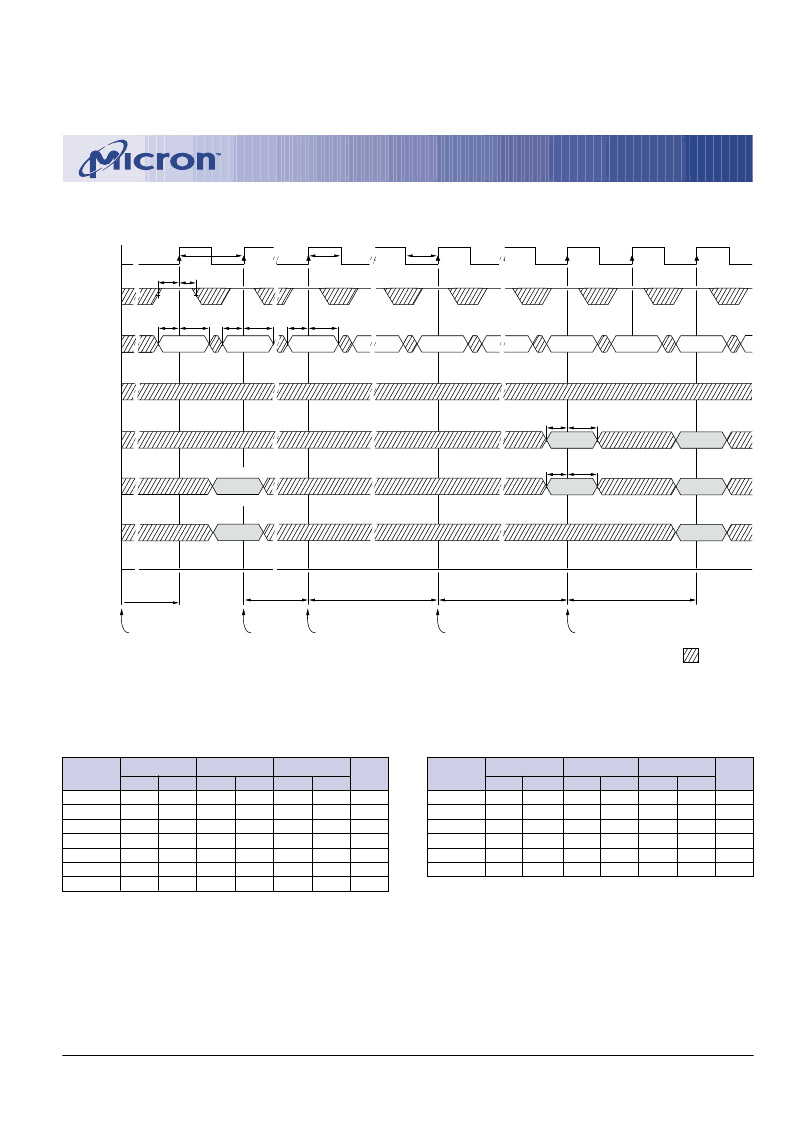

INITIALIZE AND LOAD MODE REGISTER

1

*CAS latency indicated in parentheses.

NOTE:

1. If CS# is HIGH at clock HIGH time, all commands applied are NOP, with CKE a

“

Don

’

t Care.

”

2. The mode register may be loaded prior to the AUTO REFRESH cycles if desired.

3. JEDEC and PC100 specify three clocks.

4. Outputs are guaranteed High-Z after command is issued.

-7E

-75

-8E

SYMBOL*

t

CKS

t

CMH

t

CMS

t

MRD

3

t

RFC

t

RP

MIN

1.5

0.8

1.5

2

66

15

MAX

MIN

1.5

0.8

1.5

2

66

20

MAX

MIN

2

1

2

2

70

20

MAX

UNITS

ns

ns

ns

t

CK

ns

ns

TIMING PARAMETERS

-7E

-75

-8E

SYMBOL*

t

AH

t

AS

t

CH

t

CL

t

CK (3)

t

CK (2)

t

CKH

MIN

0.8

1.5

2.5

2.5

7

7.5

0.8

MAX

MIN

0.8

1.5

2.5

2.5

7.5

10

0.8

MAX

MIN

1

2

3

3

8

10

1

MAX

UNITS

ns

ns

ns

ns

ns

ns

ns

tCH

tCL

tCK

CKE

CLK

COMMAND

DQ

BA0, BA1

BANK

tRFC

tMRD

tRFC

AUTO REFRESH

AUTO REFRESH

Program Mode Register

2, 3, 4

tCMH

tCMS

Precharge

all banks

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

tRP

(

)

(

)

(

)

(

)

tCKS

Power-up:

V

DD

and

CLK stable

T = 100μs

MIN

PRECHARGE

NOP

RAUTO

NOP

LREGISTER

ACTIVE

NOP

NOP

NOP

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

RAUTO

ALL

BANKS

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

High-Z

tCKH

(

)

(

)

(

)

(

)

DQM /

DQML, DQMH

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

()()

()()

()()

()()

()()

NOP

(

)

(

)

(

)

(

)

tCMH

tCMS

tCMH

tCMS

A0-A9, A11

ROW

tAH

tAS

CODE

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

A10

ROW

tAH

tAS

CODE

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

ALL BANKS

SINGLE BANK

(

)

(

)

(

)

(

)

(

)

(

)

(

)

(

)

DON

’

T CARE

T0

T1

Tn + 1

To + 1

Tp + 1

Tp + 2

Tp + 3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT48LC8M16A2TG-7EIT | SYNCHRONOUS DRAM |

| MT48LC8M16A2TG-7EL | SYNCHRONOUS DRAM |

| MT48LC8M16A2TG-7ELIT | SYNCHRONOUS DRAM |

| MT48LC8M16A2TG-8E | SYNCHRONOUS DRAM |

| MT48LC8M16A2TG-8EIT | SYNCHRONOUS DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。