- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383640 > MT1020A (Mitel Networks Corporation) Bluetooth Baseband Controller(藍(lán)牙技術(shù)基帶控制器) PDF資料下載

參數(shù)資料

| 型號(hào): | MT1020A |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | Bluetooth Baseband Controller(藍(lán)牙技術(shù)基帶控制器) |

| 中文描述: | 藍(lán)牙基帶控制器(藍(lán)牙技術(shù)基帶控制器) |

| 文件頁數(shù): | 3/9頁 |

| 文件大小: | 117K |

| 代理商: | MT1020A |

3

MT1020A

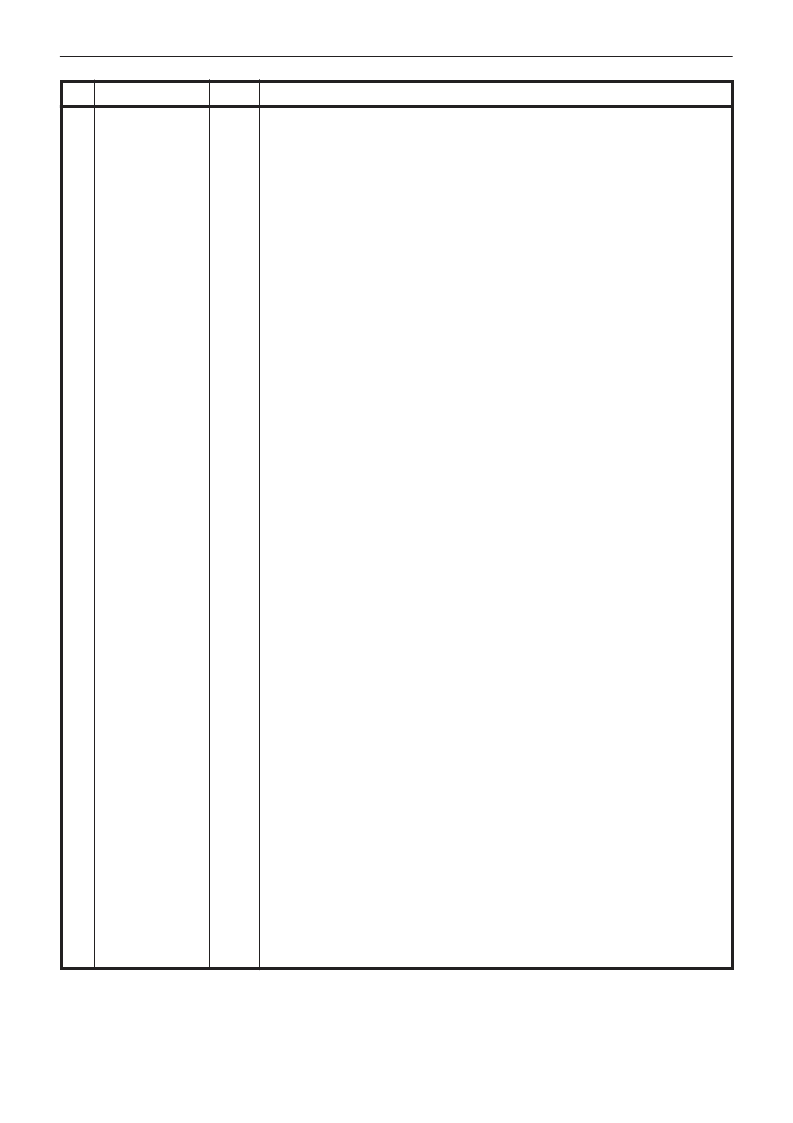

Pin

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

E1

E2

E3

E4

E5

E6

E7

E8

E9

E10

E11

F1

F2

F3

F4

F5

F6

F7

F8

F9

F10

F11

G1

G2

G3

G4

G5

G6

G7

G8

G9

G10

G11

H1

H2

H3

H4

H5

H6

H7

H8

Name

nSub

Sadd<18>

Sdata<9>

Hst_uart_txd

Sdata<3>

Sdata<8>

Sdata<6>

Gpio<1>

Gpio<2>

GND

LaV

DD

U1cts

U1txd

Sadd<0>

PLL_at1

nScs<0>

Sdata<4>

Gpio<3>

Gpio<4>

Gpio<5>

LaV

DD

GND

Lin_pcm_in

U1rxd

U1rts

Lin_pcm_out

Gpio<6>

Sdata<14>

Gpio<7>

Sdata<7>

Swait

OpV

DD

LaV

DD

Lin_pcm_clk

Lin_pcm_frm

Tdo_bdiag_2

Tck_bdiag_0

Ri _ txd

Ri_rx_act

Sadd<6>

Sadd<2>

Sadd<7>

GND

OpV

DD

Tdi_bdiag_1

Tms_bdiag_3

Sadd<8>

Ri_tx_en

Ri_spi_clk

Ri_spi_en

Test

Type

O

O

I/O (hd)

O

I/O (hd)

I/O (hd)

I/O (hd)

I/O

I/O

I

O

O

O

I/O (hd)

I/O

I/O

I/O

I

I

O

O

I/O

I/O (hd)

I/O

I/O (hd)

I (pd)

O

O

O

I

O

I

O

O

O

I/O

I/O

O

O

O

O

I (pd)

Description

System Upper Byte (for 16-bit RAM, Sadd<0> = lower byte), active low

System Address (19-bit bus)

System Data (15-bit bus)

Serial Host Interface Transmit Data

System Data (15-bit bus)

System Data (15-bit bus)

System Data (15-bit bus)

General purpose l/O

General purpose l/O

Common Ground

Core V

DD

Power Supply

UART1 Clear to Send

UART1 Transmit Data

System Address (19-bit bus)

Phase Lock Loop 1 Analog Test Pin

System Chip Select, active low

System Data (15-bit bus)

General purpose l/O plus optional USB Wake output

General purpose I/O plus optional USB HPWR output

General purpose l/O plus optional USB HPWR input

Core V

DD

Power Supply

Common Ground

16-bit Linear PCM Input stream

UART1 Receive Data

UART1 Ready to Send

16-bit Linear PCM Output stream

General purpose l/O plus external interrupt 2

System Data (15-bit bus)

General purpose l/O plus external interrupt 1

System Data (15-bit bus)

System Wait

System l/O V

DD

Core V

DD

Power Supply

16-bit Linear PCM Clock Master Output / Slave Input

16-bit Linear PCM Frame Sync Master Output / Slave Input

ICE Test data output or Xdiag<2> output

ICE Test clock input or Xdiag<0> output

Radio Transmit Data

Radio Receive Active. Start demodulating receive data

System Address (19-bit bus)

System Address (19-bit bus)

System Address (19-bit bus)

Common Ground

System l/O V

DD

ICE Test data input or Xdiag<1> output

ICE Scan test mode Input or Xdiag<3> output

System Address (19-bit bus)

Radio Transmit Enable

Radio Serial Interface Clock

Radio Serial Interface Enable

Test Enable

Table 1 Pin descriptions (continued); note: hd = internal hold cell, pd = internal pull-down

cont

…

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT24061 | MT24076 ARINC629 PROTOCOL |

| MT25001 | ARINC629 RECEIVER/MONITOR |

| MT25003 | ARINC629 RECEIVER TRANSMITTER |

| MT3170BE | Wide Dynamic Range DTMF Receiver |

| MT3170 | Wide Dynamic Range DTMF Receiver |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT10-2403S | 制造商:VOLGEN 制造商全稱:VOLGEN 功能描述:10 WATT DC//DC CONVERTER,, SIINGLE & MULTIIPLE OUTPUTS |

| MT10-2405S | 制造商:VOLGEN 制造商全稱:VOLGEN 功能描述:10 WATT DC//DC CONVERTER,, SIINGLE & MULTIIPLE OUTPUTS |

| MT10-2412S | 制造商:VOLGEN 制造商全稱:VOLGEN 功能描述:10 WATT DC//DC CONVERTER,, SIINGLE & MULTIIPLE OUTPUTS |

| MT10-2412W | 制造商:VOLGEN 制造商全稱:VOLGEN 功能描述:10 WATT DC//DC CONVERTER,, SIINGLE & MULTIIPLE OUTPUTS |

| MT10-2415S | 制造商:VOLGEN 制造商全稱:VOLGEN 功能描述:10 WATT DC//DC CONVERTER,, SIINGLE & MULTIIPLE OUTPUTS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。