- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45383 > MR80C52CXXX-25SB (TEMIC SEMICONDUCTORS) 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CQCC44 PDF資料下載

參數(shù)資料

| 型號(hào): | MR80C52CXXX-25SB |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CQCC44 |

| 文件頁數(shù): | 7/60頁 |

| 文件大小: | 5137K |

| 代理商: | MR80C52CXXX-25SB |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

15

8266D-MCU Wireless-06/12

ATmega128RFA1

7.7 Instruction Execution Timing

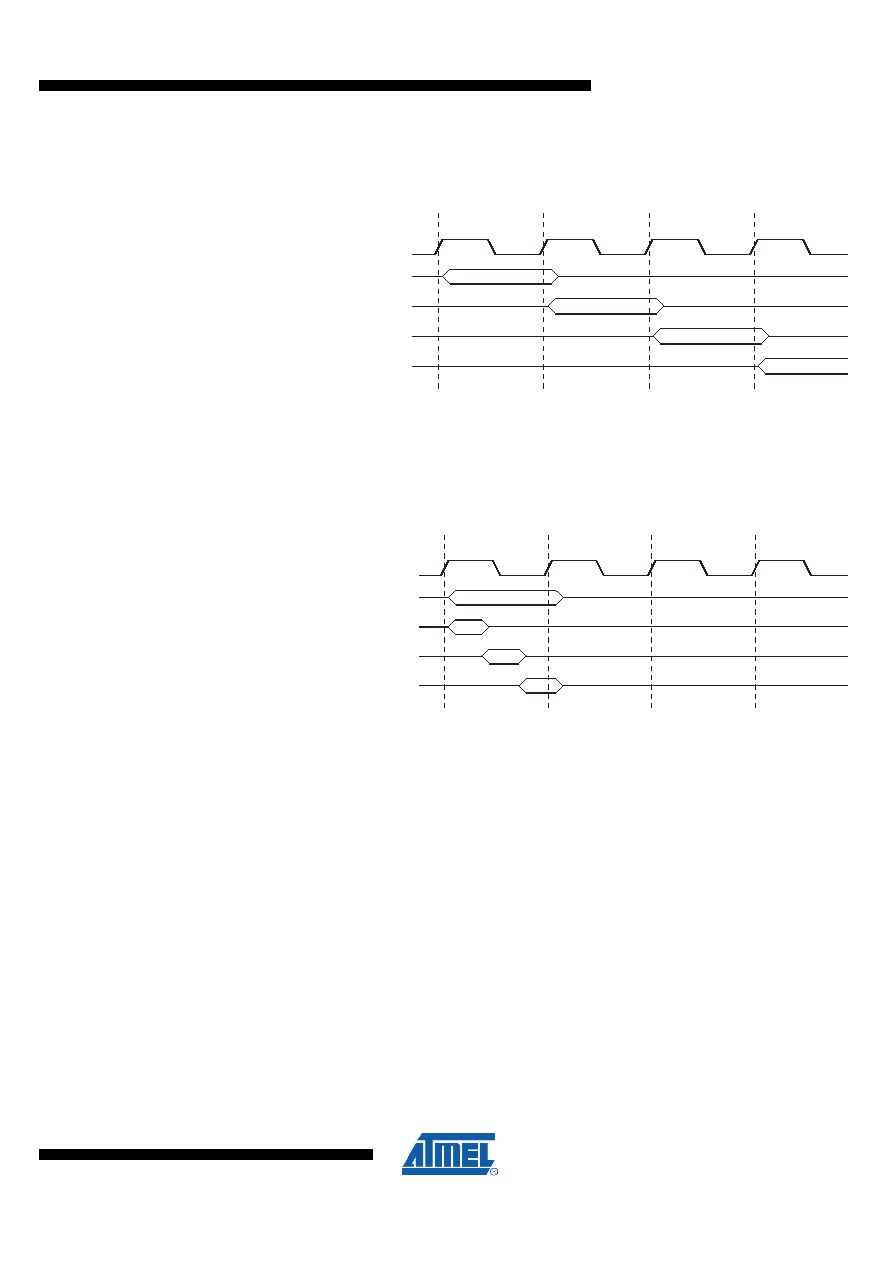

Figure 7-4. The Parallel Instruction Fetches and Instruction Executions

clk

1st Instruction Fetch

1st Instruction Execute

2nd Instruction Fetch

2nd Instruction Execute

3rd Instruction Fetch

3rd Instruction Execute

4th Instruction Fetch

T1

T2

T3

T4

CPU

Figure 7-5 below shows the internal timing concept for the Register File. In a single

clock cycle an ALU operation using two register operands is executed, and the result is

stored back to the destination register.

Figure 7-5. Single Cycle ALU operation

Total Execution Time

Register Operands Fetch

ALU Operation Execute

Result Write Back

T1

T2

T3

T4

clk

CPU

7.8 Reset and Interrupt Handling

The AVR provides several different interrupt sources. These interrupts and the separate

Reset Vector each have a separate program vector in the program memory space. All

interrupts are assigned individual enable bits which must be written logic one together

with the Global Interrupt Enable bit in the Status Register in order to enable the

interrupt. Depending on the Program Counter value, interrupts may be automatically

disabled when Boot Lock bits BLB02 or BLB12 are programmed. This feature improves

software security. See the section "Memory Programming" on page 469 for details.

The lowest addresses in the program memory space are by default defined as the

Reset and Interrupt Vectors. The complete list of vectors is shown in "Interrupts" on

page 214. The list also determines the priority levels of the different interrupts. The

lower the address the higher is the priority level. RESET has the highest priority, and

next is INT0 – the External Interrupt Request 0. The Interrupt Vectors can be moved to

the start of the Boot Flash section by setting the IVSEL bit in the MCU Control Register

(MCUCR). Refer to "Interrupts" on page 214 for more information. The Reset Vector

can also be moved to the start of the Boot Flash section by programming the

BOOTRST Fuse, see "Memory Programming" on page 469.

When an interrupt occurs, the Global Interrupt Enable I-bit is cleared and all interrupts

are disabled. The user software can write logic one to the I-bit to enable nested

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MR80C52UXXX-25 | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CQCC44 |

| IS80C32U-S | 8-BIT, 20 MHz, MICROCONTROLLER, PQCC44 |

| IV80C52UXXX-S | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, PQFP44 |

| IS80C52UFXXX-S:R | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, PQCC44 |

| IS80C52UXXX-25:R | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, PQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MR80C86 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86/B | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Harris Corporation 功能描述:Microprocessor, 16 Bit, 44 Pin, Ceramic, LCC |

| MR80C86-2 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MR80C86-2/883 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MR80C86-2/B | 制造商:Intersil Corporation 功能描述:MPU 80C86 16BIT CMOS 8MHZ 44PLCC - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。