- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359669 > MC9328MXLVP20 (飛思卡爾半導(dǎo)體(中國(guó))有限公司) i.MX Integrated Portable System Processor PDF資料下載

參數(shù)資料

| 型號(hào): | MC9328MXLVP20 |

| 廠商: | 飛思卡爾半導(dǎo)體(中國(guó))有限公司 |

| 元件分類: | 微處理器 |

| 英文描述: | i.MX Integrated Portable System Processor |

| 中文描述: | i.MX處理器集成的便攜式系統(tǒng) |

| 文件頁(yè)數(shù): | 90/96頁(yè) |

| 文件大?。?/td> | 1495K |

| 代理商: | MC9328MXLVP20 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)當(dāng)前第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)

MC9328MX1 Advance Information, Rev. 4

90

Freescale Semiconductor

Specifications

The limitation on pixel clock rise time / fall time are not specified. It should be calculated from the hold time and

setup time, according to:

Rising-edge latch data

max rise time allowed = (positive duty cycle - hold time)

max fall time allowed = (negative duty cycle - setup time)

In most of case, duty cycle is 50 / 50, therefore

max rise time = (period / 2 - hold time)

max fall time = (period / 2 - setup time)

For example: Given pixel clock period = 10ns, duty cycle = 50 / 50, hold time = 1ns, setup time = 1ns.

positive duty cycle = 10 / 2 = 5ns

=> max rise time allowed = 5 - 1 = 4ns

negative duty cycle = 10 / 2 = 5ns

=> max fall time allowed = 5 - 1 = 4ns

Falling-edge latch data

max fall time allowed = (negative duty cycle - hold time)

max rise time allowed = (positive duty cycle - setup time)

3.22.2 Non-Gated Clock Mode

Figure 70 shows the timing diagram when the CMOS sensor output data is configured for negative edge and the

CSI is programmed to received data on the positive edge. Figure 71 on page 91 shows the timing diagram when the

CMOS sensor output data is configured for positive edge and the CSI is programmed to received data in negative

edge. The parameters for the timing diagrams are listed in Table 43 on page 91.

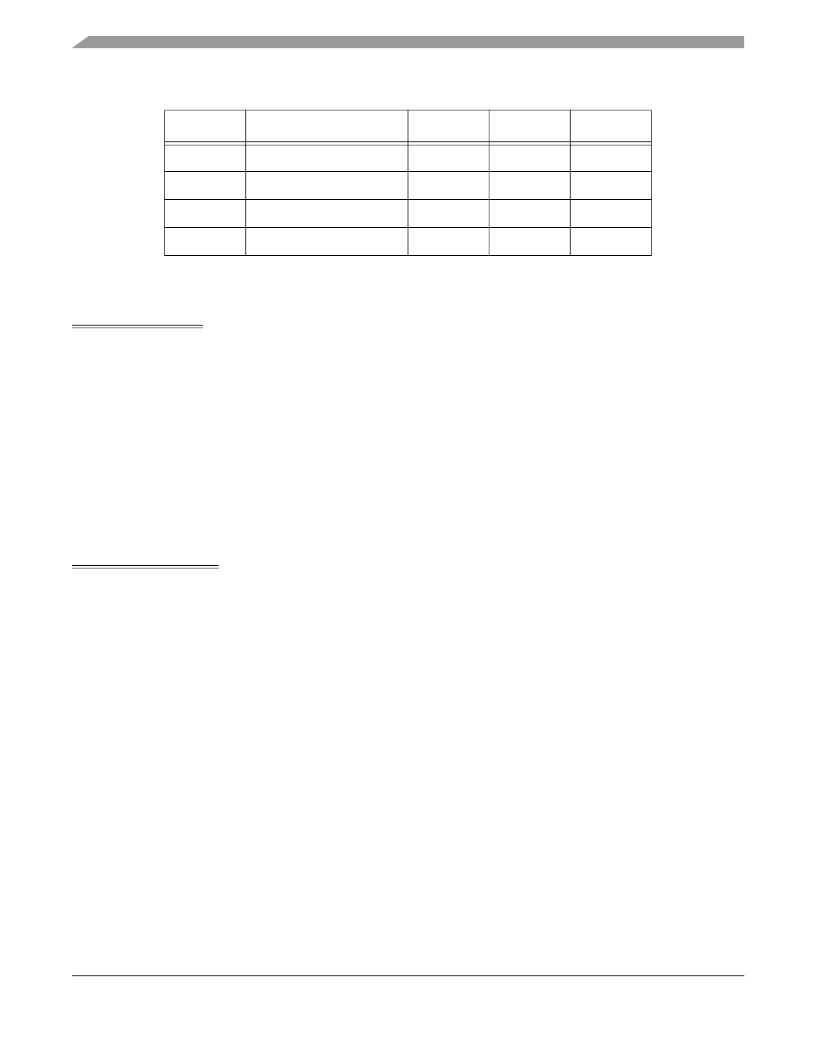

4

csi_d hold time

1

–

ns

5

csi_pixclk high time

10.42

–

ns

6

csi_pixclk low time

10.42

–

ns

7

csi_pixclk frequency

0

48

MHz

Table 42. Gated Clock Mode Timing Parameters (Continued)

Ref No.

Parameter

Minimum

Maximum

Unit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC9328MXLDVF20 | i.MX Integrated Portable System Processor |

| MC9328MXLDVH20 | i.MX Integrated Portable System Processor |

| MC9328MXLDVM20 | i.MX Integrated Portable System Processor |

| MC9328MXLDVP20 | i.MX Integrated Portable System Processor |

| MC9S12DJ256B | device made up of standard HCS12 blocks and the HCS12 processor core |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC9328MXLVP20R2 | 功能描述:處理器 - 專門應(yīng)用 DRAGONBALL MXL 225 PB-FR RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| MC9328MXS | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Advance Information |

| MC9328MXSCVF10 | 制造商:Rochester Electronics LLC 功能描述:REDUCED FEATURE I.MXL - Bulk 制造商:Freescale Semiconductor 功能描述: 制造商:Motorola Inc 功能描述: |

| MC9328MXSCVF10(R2) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Advance Information |

| MC9328MXSCVF10R2 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Advance Information |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。