- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384688 > MAX5863ETM (MAXIM INTEGRATED PRODUCTS INC) 5V High-Speed RS-232 Transceivers with 0.1uF Capacitors PDF資料下載

參數(shù)資料

| 型號(hào): | MAX5863ETM |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 無繩電話/電話 |

| 英文描述: | 5V High-Speed RS-232 Transceivers with 0.1uF Capacitors |

| 中文描述: | TELECOM, CELLULAR, RF AND BASEBAND CIRCUIT, QCC48 |

| 封裝: | 7 X 7 MM, 0.80 MM HEIGHT, TQFN-48 |

| 文件頁數(shù): | 5/26頁 |

| 文件大小: | 1673K |

| 代理商: | MAX5863ETM |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

M

Ultra-Low-Power, High-Dynamic

Performance, 7.5Msps Analog Front End

_______________________________________________________________________________________

5

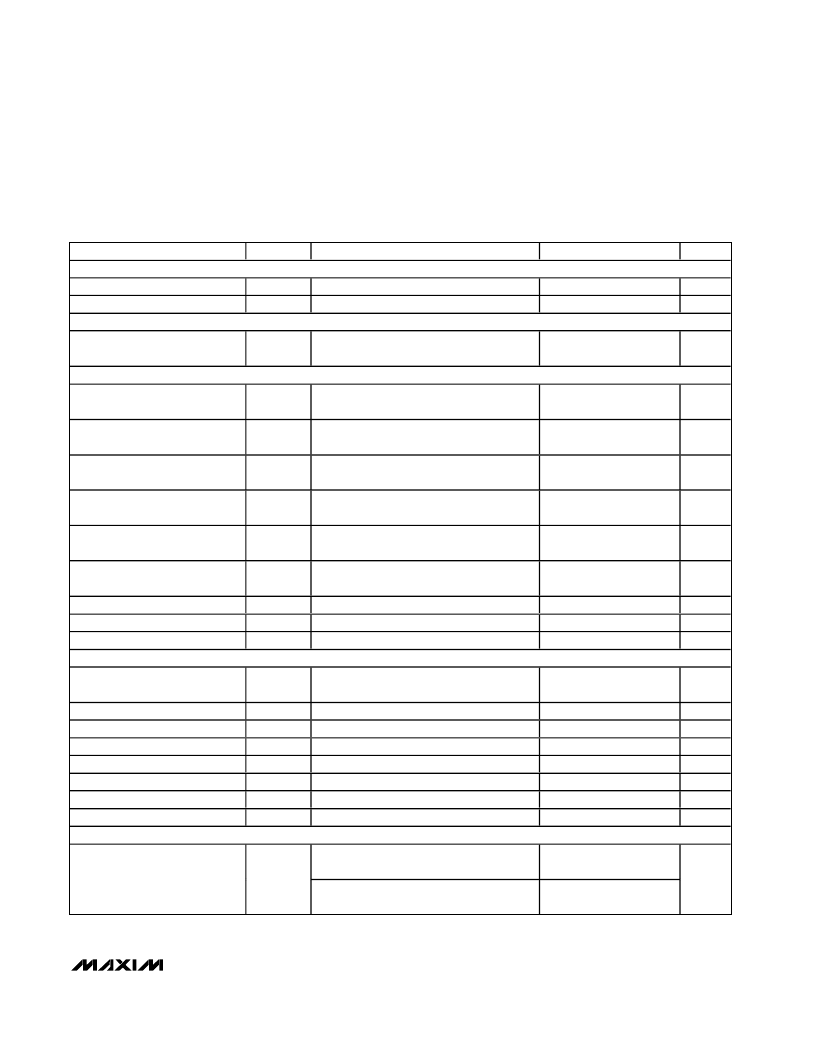

ELECTRICAL CHARACTERISTICS (continued)

(V

DD

= 3V, OV

DD

= 1.8V, internal reference (1.024V), C

L

≈

10pF on all digital outputs, f

CLK

= 7.5MHz, ADC input amplitude = -0.5dBFS,

DAC output amplitude = 0dBFS, differential ADC input, differential DAC output, C

REFP

= C

REFN

= C

COM

= 0.33μF, Xcvr mode, unless

otherwise noted. Typical values are at T

A

= +25

°

C, unless otherwise noted.) (Note 1)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

DAC ANALOG OUTPUT

Full-Scale Output Voltage

Output Common-Mode Range

ADC-DAC INTERCHANNEL CHARACTERISTICS

V

FS

±

400

mV

V

1. 29

1. 5

ADC-DAC Isolation

ADC f

INI

= f

INQ

= 1.875MHz, DAC f

OUTI

=

f

OUTQ

= 620kHz, f

CLK

= 7.5MHz

75

dB

ADC-DAC TIMING CHARACTERISTICS

CLK Rise to I-ADC Channel-I

Output Data Valid

t

DOI

Figure 3 (Note 4)

7.4

9

ns

CLK Fall to Q-ADC Channel-Q

Output Data Valid

t

DOQ

Figure 3 (Note 4)

6.9

9

ns

I-DAC Data to CLK Fall Setup

Time

t

DSI

Figure 4 (Note 4)

10

ns

Q-DAC Data to CLK Rise Setup

Time

t

DSQ

Figure 4 (Note 4)

10

ns

CLK Fall to I-DAC Data Hold

Time

t

DHI

Figure 4 (Note 4)

0

ns

CLK rise to Q-DAC Data Hold

Time

t

DHQ

Figure 4 (Note 4)

0

ns

Clock Duty Cycle

CLK Duty-Cycle Variation

Digital Output Rise/Fall Time

SERIAL INTERFACE TIMING CHARACTERISTICS

50

±

15

2.6

%

%

ns

20% to 80%

Falling Edge of

CS

to Rising

Edge of First SCLK Time

t

CSS

Figure 5 (Note 4)

10

ns

DIN to SCLK Setup Time

DIN to SCLK Hold Time

SCLK Pulse Width High

SCLK Pulse Width Low

SCLK Period

SCLK to

CS

Setup Time

CS

High Pulse Width

MODE RECOVERY TIMING CHARACTERISTICS

t

DS

t

DH

t

CH

t

CL

t

CP

t

CS

t

CSW

Figure 5 (Note 4)

Figure 5 (Note 4)

Figure 5 (Note 4)

Figure 5 (Note 4)

Figure 5 (Note 4)

Figure 5 (Note 4)

Figure 5 (Note 4)

10

0

25

25

50

0

80

ns

ns

ns

ns

ns

ns

ns

From shutdown to Rx mode, Figure 6, ADC

settles to within 1dB

20

Shutdown Wake-Up Time

t

WAKE,SD

From shutdown to Tx mode, Figure 6, DAC

settles to within 10 LSB error.

40

μs

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX5864 | Quadruple Differential Line Receiver 16-CDIP -55 to 125 |

| MAX5864ETM | Ultra-Low-Power, High-Dynamic- Performance, 22Msps Analog Front End |

| MAX5865 | Ultra-Low-Power, High-Dynamic- Performance, 40Msps Analog Front End |

| MAX5865ETM | Ultra-Low-Power, High-Dynamic- Performance, 40Msps Analog Front End |

| MAX5873 | Quadruple Line Driver 14-CDIP -55 to 125 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX5863ETM+ | 功能描述:ADC / DAC多通道 10-Bit 2Ch 7.5Msps CODEC/AFE RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率: 分辨率:8 bit 接口類型:SPI 電壓參考: 電源電壓-最大:3.6 V 電源電壓-最小:2 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-40 |

| MAX5863ETM+T | 功能描述:ADC / DAC多通道 RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率: 分辨率:8 bit 接口類型:SPI 電壓參考: 電源電壓-最大:3.6 V 電源電壓-最小:2 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-40 |

| MAX5863ETM-T | 功能描述:ADC / DAC多通道 RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率: 分辨率:8 bit 接口類型:SPI 電壓參考: 電源電壓-最大:3.6 V 電源電壓-最小:2 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-40 |

| MAX5864ETM | 功能描述:ADC / DAC多通道 RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率: 分辨率:8 bit 接口類型:SPI 電壓參考: 電源電壓-最大:3.6 V 電源電壓-最小:2 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-40 |

| MAX5864ETM+ | 功能描述:ADC / DAC多通道 10-Bit 2Ch 22Msps CODEC/AFE RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換速率: 分辨率:8 bit 接口類型:SPI 電壓參考: 電源電壓-最大:3.6 V 電源電壓-最小:2 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-40 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。