- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1938 > MAX3109ETJ+ (Maxim Integrated Products)SEMICONDUCTOR OTHER PDF資料下載

參數(shù)資料

| 型號(hào): | MAX3109ETJ+ |

| 廠商: | Maxim Integrated Products |

| 文件頁數(shù): | 33/66頁 |

| 文件大?。?/td> | 0K |

| 描述: | SEMICONDUCTOR OTHER |

| 標(biāo)準(zhǔn)包裝: | 60 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當(dāng)前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

Dual Serial UART with 128-Word FIFOs

MAX3109

39

Maxim Integrated

MODE2 Register

Bit 7: EchoSuprs

Set the EchoSuprs bit high to discard any data that the MAX3109 receives when its transmitter is busy transmit-

ting. In half-duplex communication such as RS-485 and IrDA, this allows blocking of the locally echoed data. The

receiver can block data for an extended time after the transmitter ceases transmission by programming a hold time in

HDplxDelay[3:0].

Bit 6: MultiDrop

Set the MultiDrop bit high to enable the 9-bit multidrop mode. If this bit is set, parity checking is not performed by the

receiver and parity generation is not done by the transmitter. The address/data indication takes the place of the parity

bit in received and transmitted data words. The parity error interrupt in LSR[2] has a different meaning in multidrop

mode: it represents the 9th bit (address/data indication) that is received with each 9-bit data character.

Bit 5: Loopback

Set the Loopback bit high to enable internal local loopback mode. This internally connects TX_ to RX_ and also RTS_

to CTS_. In local loopback mode, the TX_ output and the RX_ input are disconnected from the internal transmitter and

receiver. The TX_ output is in three-state. The RTS_ output remains connected to the internal logic and reflects the logic

state programmed in LCR[7]. The CTS_ input is disconnected from RTS_ and the internal logic. CTS_ thus remains in

a high-impedance state.

Bit 4: SpecialChr

Set the SpecialChr bit high to enable special character detection. The receiver can detect up to four special characters,

as selected in FlowCtrl[5:4] and defined in the XON1, XON2, XOFF1, and/or XOFF2 registers, optionally in combina-

tion with GPIO_ inputs if enabled through FlowCtrl[2]: GPIAddr. When a special character is received, it is put into the

RxFIFO and a special character detect interrupt is generated in ISR[1].

Special character detection can be used in addition to auto XON/XOFF flow control if enabled by FlowCtrl[3]:

SwFlowEn. In this case, XON/XOFF flow control is limited to single byte XON and XOFF characters (XON1 and XOFF1),

and only two special characters can be defined (XON2 and XOFF2).

Bit 3: RFifoEmtyInv

Set the RFifoEmtyInv bit high to invert the meaning of the receiver empty interrupt in ISR[6]: RxEmptyInt. If RFifoEmtyInv

is set low, RxEmptyInt is generated when the receive FIFO is empty. If RFifoEmtyInv is set high, RxEmptyInt is gener-

ated when data is put into the empty receive FIFO.

Bit 2: RxTrigInv

Set the RxTrigInv bit high to invert the meaning of the RxFIFO triggering. If the RxTrgInv bit is set low, an interrupt

is generated in ISR[3]: RxTrigInt when the RxFIFO fill level is filled up to above the trigger level programmed into

FIFOTrgLvl[7:4]. If RxTrigInv is set high, an interrupt is generated in ISR[3] when the RxFIFO is emptied to below the

trigger level programmed into FIFOTrgLvl[7:4].

Bit 1: FIFORst

Set the FIFORst bit high to clear all data contents from both the receive and transmit FIFOs. After a FIFO reset, set

FIFORst low to continue normal operation.

Bit 0: RST

Set the RST bit high to initiate software reset for the selected UART in the MAX3109. The I2C/SPI bus stays active dur-

ing this reset; communication with the MAX3109 is possible while RST is set. All register bits in the selected UART are

reset to their reset state and all FIFOs are cleared during a reset.

Set RST low to continue normal operation after a software reset. The MAX3109 requires reprogramming following a

software reset.

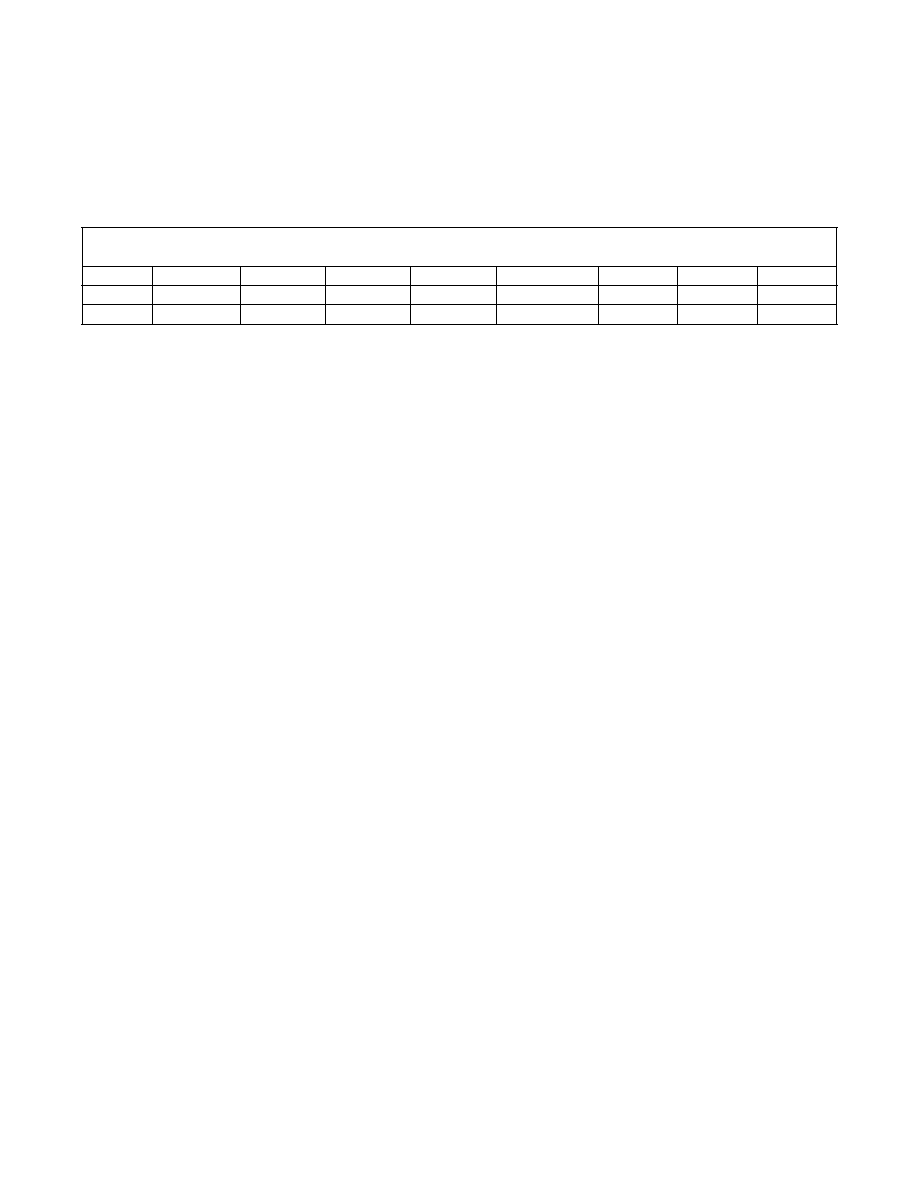

ADDRESS:

0x0A

MODE:

R/W

BIT

7

6

5

4

3

2

1

0

NAME

EchoSuprs

MultiDrop

Loopback

SpecialChr

RFifoEmptyInv

RxTrigInv

FIFORst

RST

RESET

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX310CPE | IC VIDEO MULTIPLEXER 8X1 16DIP |

| MAX3110EENI+G36 | IC UART SPI COMPAT 28-DIP |

| MAX3120CUA+ | IC TXRX INFRARED IRDA 8-UMAX |

| MAX3120EUA | IC TXRX 3V IRDA IR 3V 8-UMAX |

| MAX312ESE | IC SWITCH QUAD SPST 16SOIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX3109ETJ+ | 功能描述:UART 接口集成電路 Dual Serial UART with 128-Word FIFOs RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| MAX3109ETJ+T | 功能描述:UART 接口集成電路 Dual Serial UART with 128-Word FIFOs RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| MAX310C/D | 功能描述:多路器開關(guān) IC RoHS:否 制造商:Texas Instruments 通道數(shù)量:1 開關(guān)數(shù)量:4 開啟電阻(最大值):7 Ohms 開啟時(shí)間(最大值): 關(guān)閉時(shí)間(最大值): 傳播延遲時(shí)間:0.25 ns 工作電源電壓:2.3 V to 3.6 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UQFN-16 |

| MAX310CPE | 功能描述:多路器開關(guān) IC RoHS:否 制造商:Texas Instruments 通道數(shù)量:1 開關(guān)數(shù)量:4 開啟電阻(最大值):7 Ohms 開啟時(shí)間(最大值): 關(guān)閉時(shí)間(最大值): 傳播延遲時(shí)間:0.25 ns 工作電源電壓:2.3 V to 3.6 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UQFN-16 |

| MAX310CPE+ | 功能描述:多路器開關(guān) IC 8:1 Unbuffered RF Video MUX RoHS:否 制造商:Texas Instruments 通道數(shù)量:1 開關(guān)數(shù)量:4 開啟電阻(最大值):7 Ohms 開啟時(shí)間(最大值): 關(guān)閉時(shí)間(最大值): 傳播延遲時(shí)間:0.25 ns 工作電源電壓:2.3 V to 3.6 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UQFN-16 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。