- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383337 > MAX1813EEI (MAXIM INTEGRATED PRODUCTS INC) Dynamically-Adjustable, Synchronous Step-Down Controller with Integrated Voltage Positioning PDF資料下載

參數(shù)資料

| 型號(hào): | MAX1813EEI |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 穩(wěn)壓器 |

| 英文描述: | Dynamically-Adjustable, Synchronous Step-Down Controller with Integrated Voltage Positioning |

| 中文描述: | SWITCHING CONTROLLER, 1000 kHz SWITCHING FREQ-MAX, PDSO28 |

| 封裝: | 0.150 INCH, 0.025 INCH PITCH, QSOP-28 |

| 文件頁(yè)數(shù): | 19/38頁(yè) |

| 文件大小: | 738K |

| 代理商: | MAX1813EEI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)

M

Dynamically-Adjustable, Synchronous Step-Down

Controller with Integrated Voltage Positioning

______________________________________________________________________________________

19

put voltage in 25mV increments at the clock rate set by

R

TIME

until the MAX1813 reaches the selected output

voltage. The MAX1813 does not feature traditional vari-

able current-limit soft-start, so full output current is

immediately available. Once the slew-rate controller ter-

minates, output undervoltage fault blanking period

ends, and the output voltage is in regulation, PGOOD

goes high.

Leave SKP/

SDN

floating for forced-PWM operation, or

connect SKP/

SDN

to V

CC

for normal operation. During

all transitions, the MAX1813 uses PWM mode while the

slew-rate controller is active. Exiting shutdown clears

the fault latch.

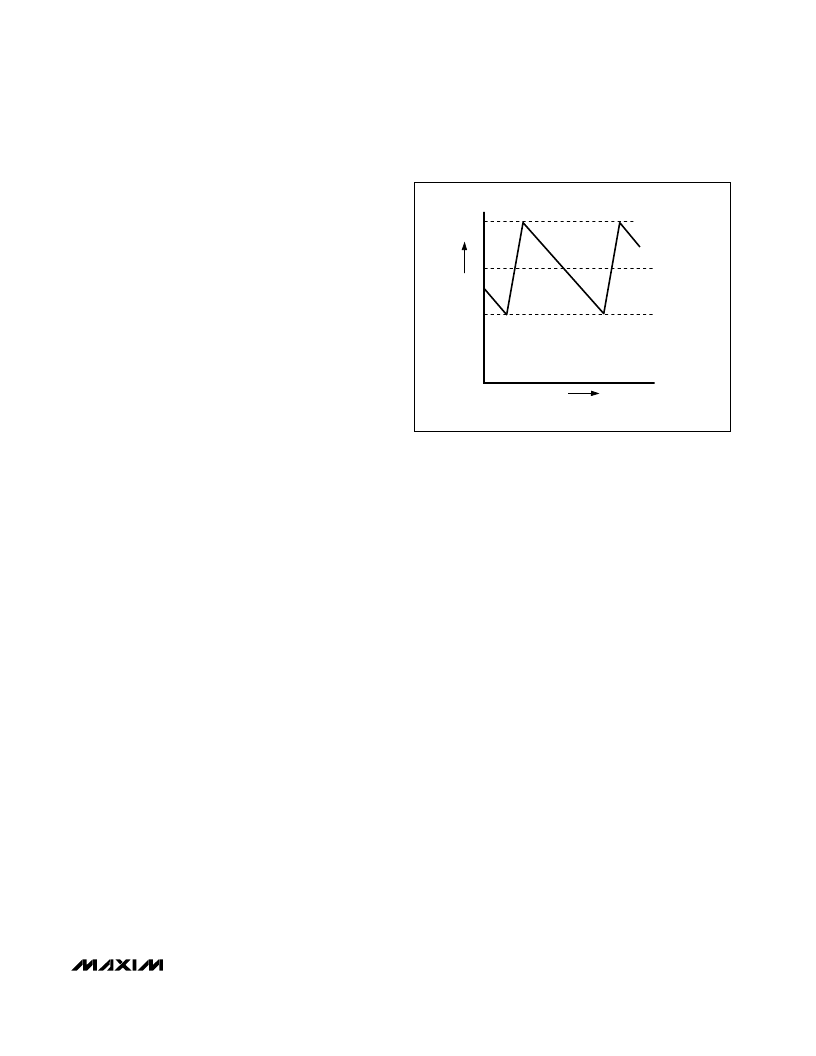

Current-Limit Circuit (ILIM)

The current-limit circuit employs a unique

“

valley

”

cur-

rent-sensing algorithm. If the current-sense signal is

above the current-limit threshold, the MAX1813 will not

initiate a new cycle (Figure 4). The actual peak current

is greater than the current-limit threshold by an amount

equal to the inductor ripple current. Therefore the exact

current-limit characteristic and maximum load capabili-

ty are a function of the current-limit threshold, inductor

value, and input voltage. The reward for this uncertainty

is robust, loss-less over-current sensing. When com-

bined with the undervoltage protection circuit, this cur-

rent-limit method is effective in almost every

circumstance.

There is also a negative current limit that prevents

excessive reverse inductor currents when V

OUT

is sink-

ing current. The negative current-limit threshold is set to

approximately 120% of the positive current limit and

therefore tracks the positive current limit when ILIM is

adjusted.

The MAX1813 measures the current by sensing the

voltage between VPCS and PGND. Connect an external

sense resistor between the source of the low-side N-

channel MOSFET and PGND. The signal provided by

this current-sense resistor is also used for voltage posi-

tioning (see

Setting Voltage Positioning

). Reducing the

sense voltage increases the relative measurement

error. However, the configuration eliminates the uncer-

tainty of using the low-side MOSFET on-resistance to

measure the current, so the resulting current-limit toler-

ance is tighter when sensing with a 1% sense resistor.

The voltage at ILIM sets the current-limit threshold. For

voltages from 500mV to 2V, the current-limit threshold

voltage is precisely 0.1 x V

ILIM

. Set this voltage with a

resistive divider between REF and GND. The current-

limit threshold defaults to 50mV when ILIM is tied to

V

CC

. The logic threshold for switchover to this 50mV

default value is approximately V

CC

- 1V.

Carefully observe the PC board layout guidelines to

ensure that noise and DC errors don

’

t corrupt the cur-

rent-sense signals seen by VPCS and GND. The IC

must be mounted close to the current-sense resistor

with short, direct traces making a Kelvin sense connec-

tion (see

PC Board Layout Guidelines

).

MOSFET Gate Drivers (DH and DL)

The DH and DL drivers are optimized for driving mod-

erate-sized, high-side and larger, low-side power

MOSFETs. This is consistent with the low duty factor

seen in the notebook CPU environment, where a large

V

IN

- V

OUT

differential exists. An adaptive dead-time

circuit monitors the DL output and prevents the high-

side FET from turning on until DL is fully off. There must

be a low-resistance, low-inductance path from the DL

driver to the MOSFET gate for the adaptive dead-time

circuit to work properly. Otherwise, the sense circuitry

in the MAX1813 will interpret the MOSFET gate as

“

off

”

while there is actually charge still left on the gate. Use

very short, wide traces (50 to 100 mils wide if the MOS-

FET is 1 inch from the device). The dead time at the

other edge (DH turning off) is determined by a fixed

35ns internal delay.

The internal pulldown transistor that drives DL low is

robust, with a 0.4

(typ) on-resistance. This helps pre-

vent DL from being pulled up during the fast rise-time

of the LX node, due to capacitive coupling from the

drain to the gate of the low-side synchronous-rectifier

MOSFET. However, for high-current applications, some

combinations of high- and low-side FETs may cause

excessive gate-drain coupling, leading to poor

I

I

LIMIT

I

LOAD

0

TIME

I

PEAK

Figure 4.

“

Valley

”

Current-Limit Threshold Point

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX1813 | Replaced by TMS320VC5506 : Digital Signal Processors 144-LQFP |

| MAX182AEWI | Calivrated 4-Channel 12-Bit ADC with T/H and Refernce |

| MAX182AEPI | Calivrated 4-Channel 12-Bit ADC with T/H and Refernce |

| MAX182BEPI | Calivrated 4-Channel 12-Bit ADC with T/H and Refernce |

| MAX182ACPI | Replaced by TMS320BC52 : Digital Signal Processors 100-LQFP -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX1813EEI+ | 功能描述:DC/DC 開(kāi)關(guān)控制器 RoHS:否 制造商:Texas Instruments 輸入電壓:6 V to 100 V 開(kāi)關(guān)頻率: 輸出電壓:1.215 V to 80 V 輸出電流:3.5 A 輸出端數(shù)量:1 最大工作溫度:+ 125 C 安裝風(fēng)格: 封裝 / 箱體:CPAK |

| MAX1813EEI+T | 功能描述:DC/DC 開(kāi)關(guān)控制器 Dynamically Adjustable Synchronous Step-Down Controller w/Integrated Voltage Positioning RoHS:否 制造商:Texas Instruments 輸入電壓:6 V to 100 V 開(kāi)關(guān)頻率: 輸出電壓:1.215 V to 80 V 輸出電流:3.5 A 輸出端數(shù)量:1 最大工作溫度:+ 125 C 安裝風(fēng)格: 封裝 / 箱體:CPAK |

| MAX1813EEI-T | 功能描述:DC/DC 開(kāi)關(guān)控制器 RoHS:否 制造商:Texas Instruments 輸入電壓:6 V to 100 V 開(kāi)關(guān)頻率: 輸出電壓:1.215 V to 80 V 輸出電流:3.5 A 輸出端數(shù)量:1 最大工作溫度:+ 125 C 安裝風(fēng)格: 封裝 / 箱體:CPAK |

| MAX1813EVKIT | 功能描述:DC/DC 開(kāi)關(guān)控制器 Evaluation Kit for the MAX1813 RoHS:否 制造商:Texas Instruments 輸入電壓:6 V to 100 V 開(kāi)關(guān)頻率: 輸出電壓:1.215 V to 80 V 輸出電流:3.5 A 輸出端數(shù)量:1 最大工作溫度:+ 125 C 安裝風(fēng)格: 封裝 / 箱體:CPAK |

| MAX1813XR46+ | 制造商:Maxim Integrated Products 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。