- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384641 > M5M4V4405CTP-6S (Mitsubishi Electric Corporation) EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM PDF資料下載

參數(shù)資料

| 型號(hào): | M5M4V4405CTP-6S |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| 中文描述: | 江戶(超頁(yè)模式)4194304位(1048576 - Word的4位)動(dòng)態(tài)隨機(jī)存儲(chǔ)器 |

| 文件頁(yè)數(shù): | 5/27頁(yè) |

| 文件大小: | 293K |

| 代理商: | M5M4V4405CTP-6S |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM

M5M4V4405CJ,TP-6,-7,-6S,-7S

MITSUBISHI LSIs

Parameter

Symbol

Limits

Unit

Min

110

60

10

48

15

Max

Min

130

70

13

55

20

Max

Parameter

Symbol

Limits

Unit

Min

Max

16.4

128

Min

Max

16.4

128

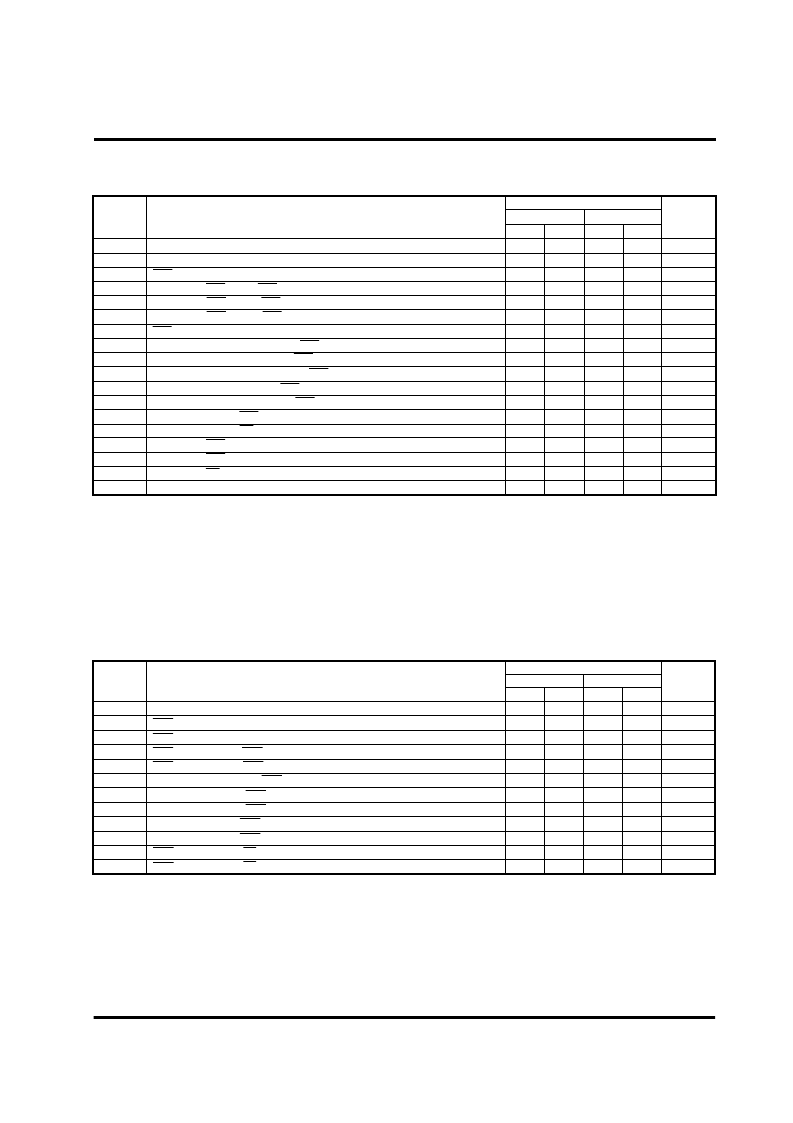

TIMING REQUIREMENTS

(Ta=0~70C, V

CC

= 3.3V±0.3V, V

SS

=0V, unless otherwise noted, see notes 14,15)

Note 14: The timing requirements are assumed

t

T

=2ns.

@

15: V

IH(min)

and V

IL(max)

are reference levels for measuring timing of input signals.

@

16:

t

RCD(max)

is specified as a reference point only. If

t

RCD

is less than

t

RCD(max

),

access time is

t

RAC

.

If

t

RCD

is greater than

t

RCD(max

),

access time is

controlled exclusively by

t

CAC

or

t

AA.

@

17:

t

RAD(max)

is specified as a reference point only. If

t

RAD

≥

t

RAD(max)

and

t

ASC

≤

t

ASC(max)

,

access time is controlled exclusively by

t

AA

.

@

18: t

ASC(max)

is specified as a reference point only. If

t

RCD

≥

t

RCD(max)

and

t

ASC

≥

t

ASC(max)

,

access time is controlled exclusively by

t

CAC

.

@

19:

Either

t

DZC

or

t

DZO

must be satisfied.

@

20: Either

t

RDD

or

t

CDD

or

t

ODD

must be satisfied.

@

21:

t

T

is measured between V

IH(min)

and V

IL(max).

(Note 21)

(Note 16)

(Note 17)

(Note 18)

45

30

0

40

20

5

13

50

10

15

0

0

10

10

0

0

15

1

(Note 19)

(Note 19)

(Note 20)

(Note 20)

(Note 20)

15

15

ms

ms

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

50

35

0

50

20

5

13

50

13

15

0

0

10

10

0

0

20

1

20

20

ns

ns

ns

ns

t

REF

t

REF

t

RP

t

RCD

t

CRP

t

RPC

t

CPN

t

RAD

t

ASR

t

ASC

t

RAH

t

CAH

t

DZC

t

DZO

t

RDD

t

CDD

t

ODD

t

T

M5M4V4405C-6,-6S

M5M4V4405C-7,-7S

Read and Refresh Cycles

Note 22: Either

t

RCH

or

t

RRH

must be satisfied for a read cycle.

(Note 22)

(Note 22)

10000

10000

0

0

0

30

18

15

15

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

10000

10000

0

0

0

35

23

20

20

t

RC

t

RAS

t

CAS

t

CSH

t

RSH

t

RCS

t

RCH

t

RRH

t

RAL

t

CAL

t

OCH

t

ORH

M5M4V4405C-6,-6S

M5M4V4405C-7,-7S

(For Read, Write, Read-Modify-Write, Refresh, and Hyper-Page Mode Cycles)

5

Refresh cycle time

Refresh cycle time

*

RAS high pulse width

Delay time, RAS low to CAS low

Delay time, CAS high to RAS low

Delay time, RAS high to CAS low

CAS high pulse width

Column address delay time from RAS low

Row address setup time before RAS low

Column address setup time before CAS low

Row address hold time after RAS low

Column address hold time after CAS low

Delay time, data to CAS low

Delay time, data to OE low

Delay time, RAS high to data

Delay time, CAS high to data

Transition time

Delay time, OE high to data

Read cycle time

RAS low pulse width

CAS low pulse width

CAS hold time after RAS low

RAS hold time after CAS low

Read Setup time before CAS low

Read hold time after CAS high

Read hold time after RAS high

Column address to RAS hold time

Column address to CAS hold time

RAS hold time after OE low

CAS hold time after OE low

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5M4V4405CTP-7 | EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M4V4405CTP-7S | EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M5256DRV-12VXL-I | 262144-BIT (32768-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5256DRV-12VLL | 262144-BIT (32768-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5256DRV-12VLL-I | 262144-BIT (32768-WORD BY 8-BIT) CMOS STATIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M5M4V4405CTP-7 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M4V4405CTP-7S | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M4V4S40CTP-12 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4M (2-BANK x 131072-WORD x 16-BIT) Synchronous DRAM |

| M5M4V4S40CTP-15 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4M (2-BANK x 131072-WORD x 16-BIT) Synchronous DRAM |

| M5M4V64S20ATP-10 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。