- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384641 > M5M4V4405CTP-6S (Mitsubishi Electric Corporation) EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM PDF資料下載

參數(shù)資料

| 型號: | M5M4V4405CTP-6S |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| 中文描述: | 江戶(超頁模式)4194304位(1048576 - Word的4位)動態(tài)隨機存儲器 |

| 文件頁數(shù): | 26/27頁 |

| 文件大?。?/td> | 293K |

| 代理商: | M5M4V4405CTP-6S |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁

EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM

M5M4V4405CJ,TP-6,-7,-6S,-7S

MITSUBISHI LSIs

refresh

cycle

read/write

cycles

read/write

cycles

refresh

cycle

refresh

cycle

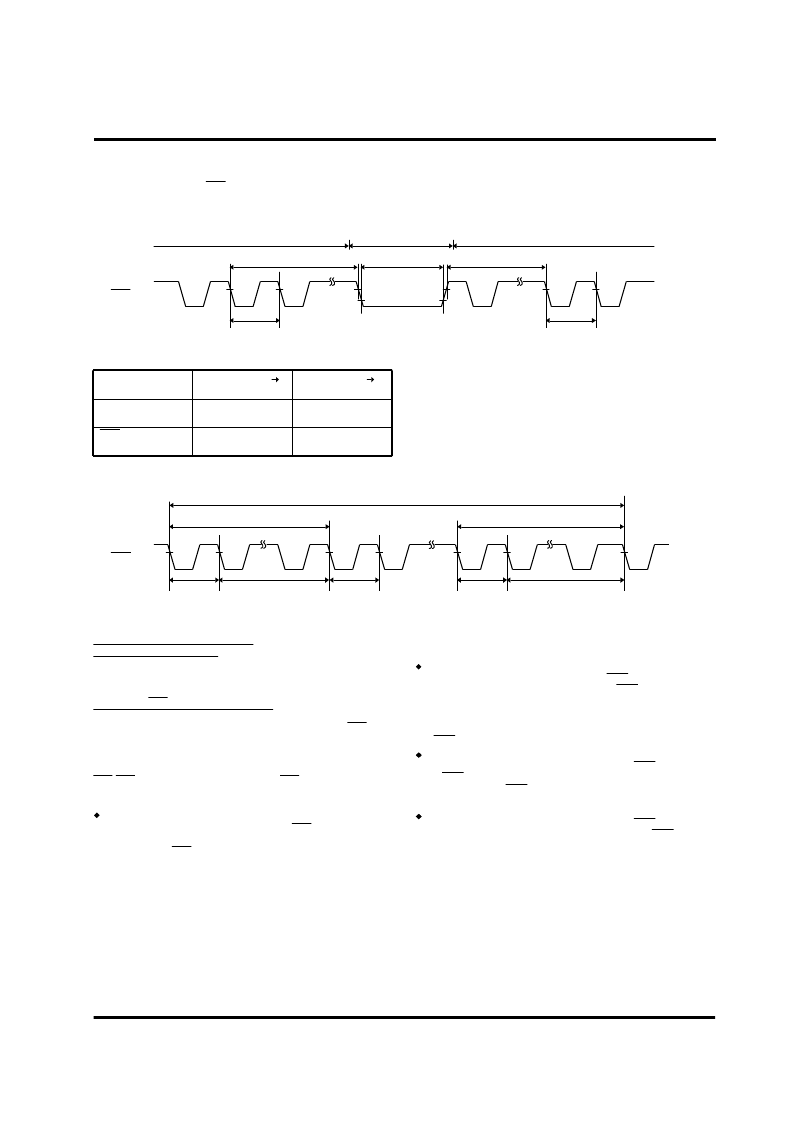

Note 30 : Self refresh sequence

Two refreshing methods should be used properly depending on the

low pulse width(t

RASS

) of RAS signal during self refresh period.

1. Distributed refresh during Read / Write operation

(A) Timing Diagram

Table 2

Read / Write Cycle

CBR distributed

refresh

RAS only

distributed refresh

Read / Write

Self Refresh

Self Refresh

Read / Write

t

NSD

≤

16μs

t

SND

≤

16μs

t

NSD

≤

125μs

t

SND

≤

125μs

Switching from read/write operation to self refresh operation.

The time interval from the falling edge of RAS signal in the last

CBR refresh cycle during read/write operation period to the

falling edge of RAS signal at the start of self refresh operation

should be set within t

NSD

(shown in table 2).

Definition of CBR distributed refresh

(Including extended refresh)

Note: Switching from read/write operation to self refresh operation.

Hidden refresh may be used instead of CBR refresh.

RAS/CAS refresh may be used instead of RAS only refresh.

1.1 CBR distributed refresh

The CBR distributed refresh performs more than 1024

constant period(125μs max.) CBR cycles within 128 ms.

All combinations of nine row address signals (A

0

~A

9

) are

selected during 1024 constant period(16μs max.) RAS only

refresh cycles within 16.4 ms.

Definition of RAS only distributed refresh

Read / Write Cycle

Self Refresh Cycle

Read / Write Cycle

t

NSD

t

RASS

≥

100μs

t

SND

last

refresh Cycle

first

refresh cycle

RAS

(B)

Definition of distributed refresh

t

REF

t

REF

/1024

RAS

t

REF

/1024

Switching from self refresh operation to read/write operation.

The time interval from the rising edge of RAS signal at the end of

self refresh operation to the falling edge of RAS signal in the first

CBR refresh cycle during read/write operation period should be

set within t

SND

(shown in table 2).

The time interval t

NSD

from the falling edge of RAS signal in the

last RAS only refresh cycle during read/write operation period to

the falling edge of RAS signal at the start of self refresh operation

should be set within 16μs.

Switching from self refresh operation to read/write operation.

The time interval t

SND

from the rising edge of RAS signal at the

end of self refresh operation to the falling edge of RAS signal in

the first CBR refresh cycle during read/write operation period

should be set within 16μs.

1.2 RAS only distributed refresh

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5M4V4405CTP-7 | EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M4V4405CTP-7S | EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M5256DRV-12VXL-I | 262144-BIT (32768-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5256DRV-12VLL | 262144-BIT (32768-WORD BY 8-BIT) CMOS STATIC RAM |

| M5M5256DRV-12VLL-I | 262144-BIT (32768-WORD BY 8-BIT) CMOS STATIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M5M4V4405CTP-7 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M4V4405CTP-7S | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M4V4S40CTP-12 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4M (2-BANK x 131072-WORD x 16-BIT) Synchronous DRAM |

| M5M4V4S40CTP-15 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4M (2-BANK x 131072-WORD x 16-BIT) Synchronous DRAM |

| M5M4V64S20ATP-10 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。