- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384641 > M5M4V4265CTP-7S (Mitsubishi Electric Corporation) EDO (HYPER PAGE) MODE 4194304-BIT (262144-WORD BY 16-BIT) DYNAMIC RAM PDF資料下載

參數(shù)資料

| 型號: | M5M4V4265CTP-7S |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | EDO (HYPER PAGE) MODE 4194304-BIT (262144-WORD BY 16-BIT) DYNAMIC RAM |

| 中文描述: | 江戶(超頁)模式4194304位(262144字由16位)動態(tài)隨機存儲器 |

| 文件頁數(shù): | 7/31頁 |

| 文件大小: | 311K |

| 代理商: | M5M4V4265CTP-7S |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

EDO (HYPER PAGE) MODE 4194304-BIT (262144-WORD BY 16-BIT) DYNAMIC RAM

M5M4V4265CJ,TP-5,-6,-7,-5S,-6S,-7S

MITSUBISHI LSIs

M5M4V4265CJ,TP-5,-5S:under development

7

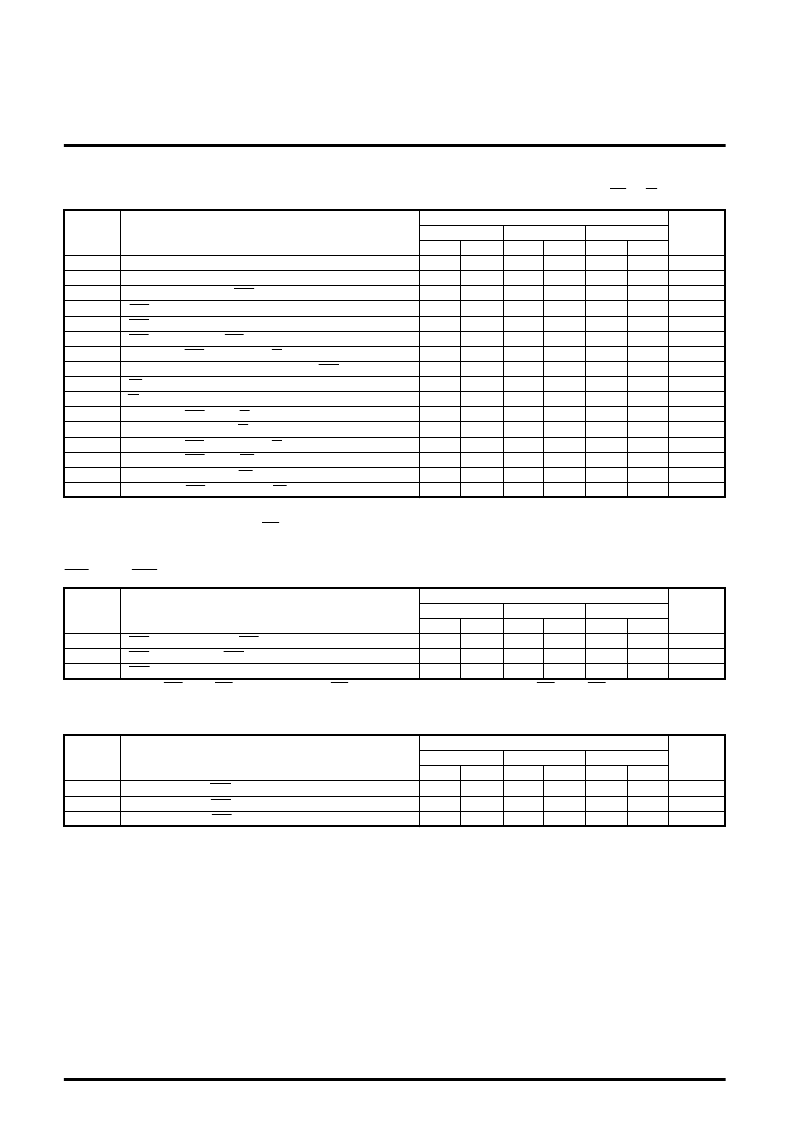

Limits

Parameter

Symbol

Unit

Min

25

66

Max

Min

30

79

5

Max

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

(Note 27)

(Note 28)

(Note 24)

16

100000

10

38

60

7

92

10

33

50

7

77

M5M4V4265C-6,-6S

M5M4V4265C-7,-7S

16

100000

Note 25 : All previously specified timing requirements and switching characteristics are applicable to their respective EDO mode cycle.

Note

26 :

t

HPC(min)

is specified in the case of read-only and early write-only in EDO mode.

Note

27 :

t

RAS(min)

is specified as two cycles of CAS input are performed.

Note

28 :

t

CP(max)

is specified as a reference point only.

Hyper page mode read/write cycle time

Hyper page mode read write/read modify write cycle time

Output hold time from CAS low

CAS high pulse width

RAS hold time after CAS precharge

Delay time, CAS precharge to W low

Hold time to maintain the data Hi-Z until CAS access

OE pulse width (Hi-Z control)

W pulse width (Hi-Z control)

Delay time, CAS low to W low after read

Delay time, Address to W low after read

Delay time, CAS precharge to W low after read

Delay time, CAS low to OE high after read

Delay time, Address to OE high after read

Delay time, CAS precharge to OE high after read

t

HPC

t

HPRWC

t

DOH

t

RAS

t

CP

t

CPRH

t

CPWD

t

CHOL

t

OEPE

t

WPE

t

HCWD

t

HAWD

t

HPWD

t

HCOD

t

HAOD

t

HPOD

(Note 26)

EDO Mode Cycle

(Read, Early Write, Read-Write, Read-Modify-Write Cycle, Read Write Mix Cycle, Hi-Z control by OE or W)

(Note 25)

42

57

60

20

32

47

50

15

35

38

30

33

5

7

7

7

7

Min

20

57

5

Max

8

65

28

43

7

M5M4V4265C-5,-5S

13

100000

28

40

43

13

25

28

7

7

Limits

Parameter

CAS setup time before RAS low

CAS hold time after RAS low

CAS low pulse width

Symbol

t

CSR

t

CHR

t

CAS

Unit

Min

5

10

17

Max

Min

5

15

22

Max

ns

ns

ns

CAS before RAS Refresh Cycle

(Note 29)

Note 29 : Eight or more CAS before RAS cycles instead of eight RAS cycles are necessary for proper operation of CAS before RAS refresh mode.

M5M4V4265C-6,-6S

M5M4V4265C-7,-7S

Min

5

10

17

Max

M5M4V4265C-5,-5S

CBR self refresh RAS low pulse width

CBR self refresh RAS high precharge time

CBR self refresh CAS hold time

t

RASS

t

RPS

t

CHS

μs

ns

100

130

-50

100

110

-50

Self Refresh Cycle

*

(Note 30)

Limits

Parameter

Symbol

Unit

Min

Max

Min

Max

ns

M5M4V4265C-6,-6S

M5M4V4265C-7,-7S

100

90

-50

Min

Max

M5M4V4265C-5,-5S

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5M4V4405CJ | EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M4V4405CTP-6 | EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M4V4405CTP-6S | EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M4V4405CTP-7 | EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M4V4405CTP-7S | EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M5M4V4405CJ | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M4V4405CJ-6 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M4V4405CJ-6S | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M4V4405CJ-7 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

| M5M4V4405CJ-7S | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:EDO (HYPER PAGE MODE) 4194304-BIT(1048576-WORD BY 4-BIT) DYNAMIC RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。