- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224146 > M470T5663EH3-CF7 DDR DRAM MODULE, ZMA200 PDF資料下載

參數(shù)資料

| 型號: | M470T5663EH3-CF7 |

| 元件分類: | DRAM |

| 英文描述: | DDR DRAM MODULE, ZMA200 |

| 封裝: | ROHS COMPLIANT, SODIMM-200 |

| 文件頁數(shù): | 20/22頁 |

| 文件大小: | 401K |

| 代理商: | M470T5663EH3-CF7 |

Rev. 1.0 August 2008

SODIMM

DDR2 SDRAM

7 of 22

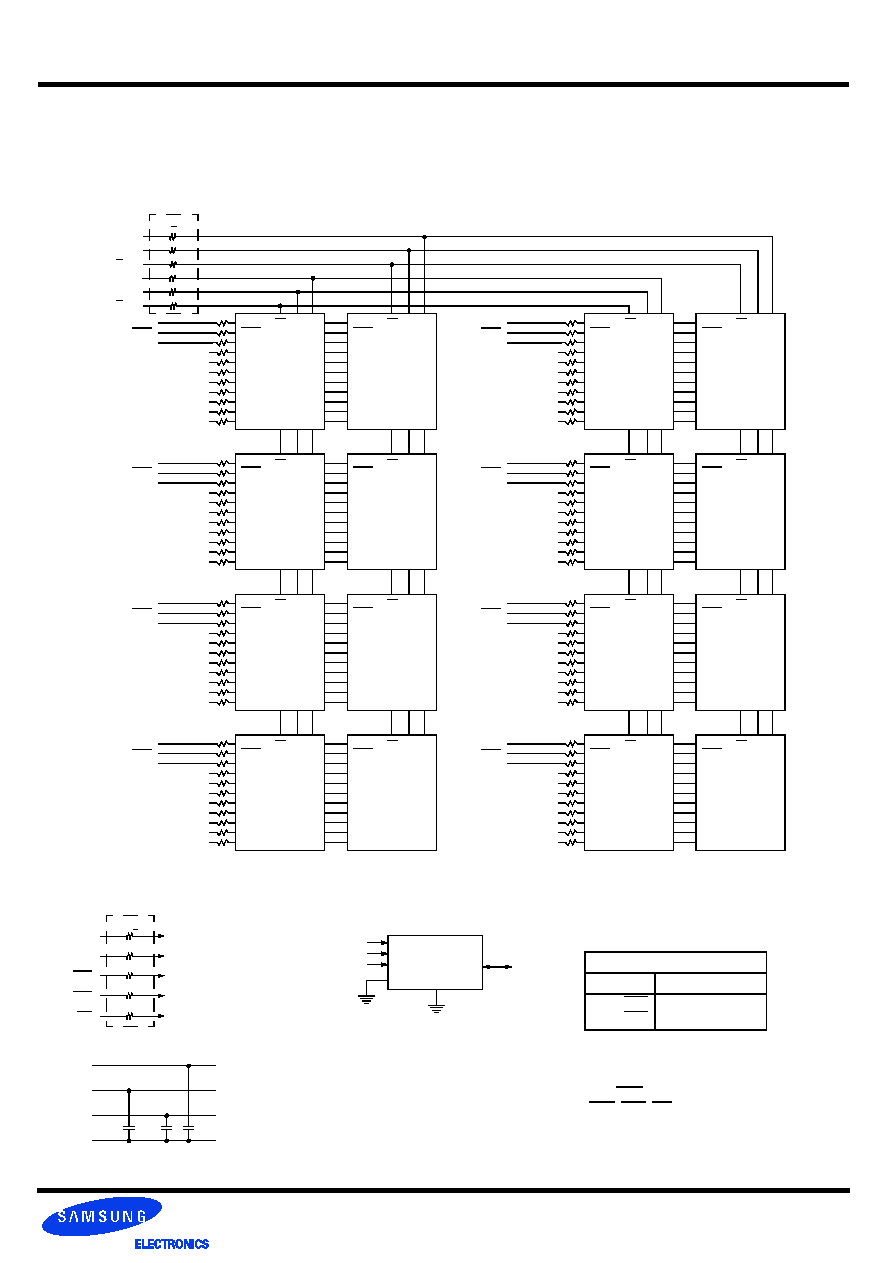

7.0 Functional Block Diagram :

(Populated as 2 ranks of x8 DDR2 SDRAMs)

7.1 2GB, 256Mx64 Module - M470T5663EH3

ODT0

CKE0

S1

ODT1

CKE1

SPD

SA0

SCL

SDA

VSS

DDR2 SDRAMs D0 - D15, SPD

REF

DDR2 SDRAMs D0 - D15

DDR2 SDRAMs D0 - D15, VDD and VDDQ

VDD

VDDSPD

Serial PD

WP

SA1

SCL

A0

A1

A2

A0 - A13

DDR2 SDRAMs D0 - D15

RAS

DDR2 SDRAMs D0 - D15

CAS

DDR2 SDRAMs D0 - D15

WE

DDR2 SDRAMs D0 - D15

BA0 - BA2

DDR2 SDRAMs D0 - D15

10

+ 5%

3

+ 5%

S0

DQS1

DM1

CS0

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D0

DQS

DM

DQS0

DM0

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

DQS

DM

DQS5

DM5

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D4

DQS

DM

DQS4

DM4

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

DQS

DM

DQS3

DM3

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DQS

DM

DQS2

DM2

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

DQS

DM

DQS7

DM7

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DQS

DM

DQS6

DM6

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

DQS

DM

O

D

T

0

C

K

E

0

CS

1

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D8

DQS

DM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

DQS

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DQS

DM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

DQS

DM

O

D

T

1

C

K

E

1

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

D12

DQS

DM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

DQS

DM

I/O 0

I/O 1

I/O 2

I/O 3

I/O 4

I/O 5

I/O 6

I/O 7

DQS

DM

I/O 8

I/O 9

I/O 10

I/O 11

I/O 12

I/O 13

I/O 14

I/O 15

DQS

DM

CS0 O

D

T

0

C

K

E

0

CS

1 O

D

T

1

C

K

E

1

CS0

D1

D5

O

D

T

0

C

K

E

0

CS

1

D9

O

D

T

1

C

K

E

1

D13

CS0 O

D

T

0

C

K

E

0

CS

1 O

D

T

1

C

K

E

1

CS0

D2

D6

O

D

T

0

C

K

E

0

CS

1

D10

O

D

T

1

C

K

E

1

D14

CS0 O

D

T

0

C

K

E

0

CS

1 O

D

T

1

C

K

E

1

CS0

D3

D7

O

D

T

0

C

K

E

0

CS

1

D11

O

D

T

1

C

K

E

1

D15

CS0 O

D

T

0

C

K

E

0

CS

1 O

D

T

1

C

K

E

1

Note :

1. DQ,DM, DQS/DQS resistors : 22 Ohms

± 5%.

2. BAx, Ax, RAS, CAS, WE resistors : 10.0 Ohms

± 5%.

* Wire per Clock Loading

Table/Wiring Diagrams

* Clock Wiring

Clock Input

DDR2 SDRAMs

*CK0/CK0

*CK1/CK1

8 DDR2 SDRAMs

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M470T6464EHS-CE6 | DDR DRAM MODULE, ZMA200 |

| M470T6464EHS-LF7 | DDR DRAM MODULE, ZMA200 |

| M48T128V | 3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| M48T12 | 16 Kbit 2Kb x8 TIMEKEEPER[ SRAM |

| M48T12-150PC1 | 16 Kbit 2Kb x8 TIMEKEEPER[ SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M470T5663FB3 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDR2 SDRAM Memory |

| M470T5663FB3-CE600 | 制造商:Samsung Semiconductor 功能描述:SDRAM DDR2, 2GB 333MHZ, 1.8V - Trays |

| M470T5663FB3-CF700 | 制造商:Samsung Semiconductor 功能描述: |

| M470T5663QZ3-CE600 | 制造商:Samsung SDI 功能描述:DRAM Module DDR2 SDRAM 2GByte 200SODIMM |

| M470T5663QZ3-CF700 | 制造商:Samsung SDI 功能描述:DRAM Module DDR2 SDRAM 2GByte 200SODIMM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。