- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299403 > LFXP20E-5FN484C (LATTICE SEMICONDUCTOR CORP) PDF資料下載

參數(shù)資料

| 型號(hào): | LFXP20E-5FN484C |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | FPGA |

| 中文描述: | FPGA, 2464 CLBS, PBGA484 |

| 封裝: | 23 X 23 MM, LEAD FREE, FPBGA-484 |

| 文件頁(yè)數(shù): | 46/130頁(yè) |

| 文件大小: | 1312K |

| 代理商: | LFXP20E-5FN484C |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)當(dāng)前第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)

2-19

Architecture

Lattice Semiconductor

LatticeXP Family Data Sheet

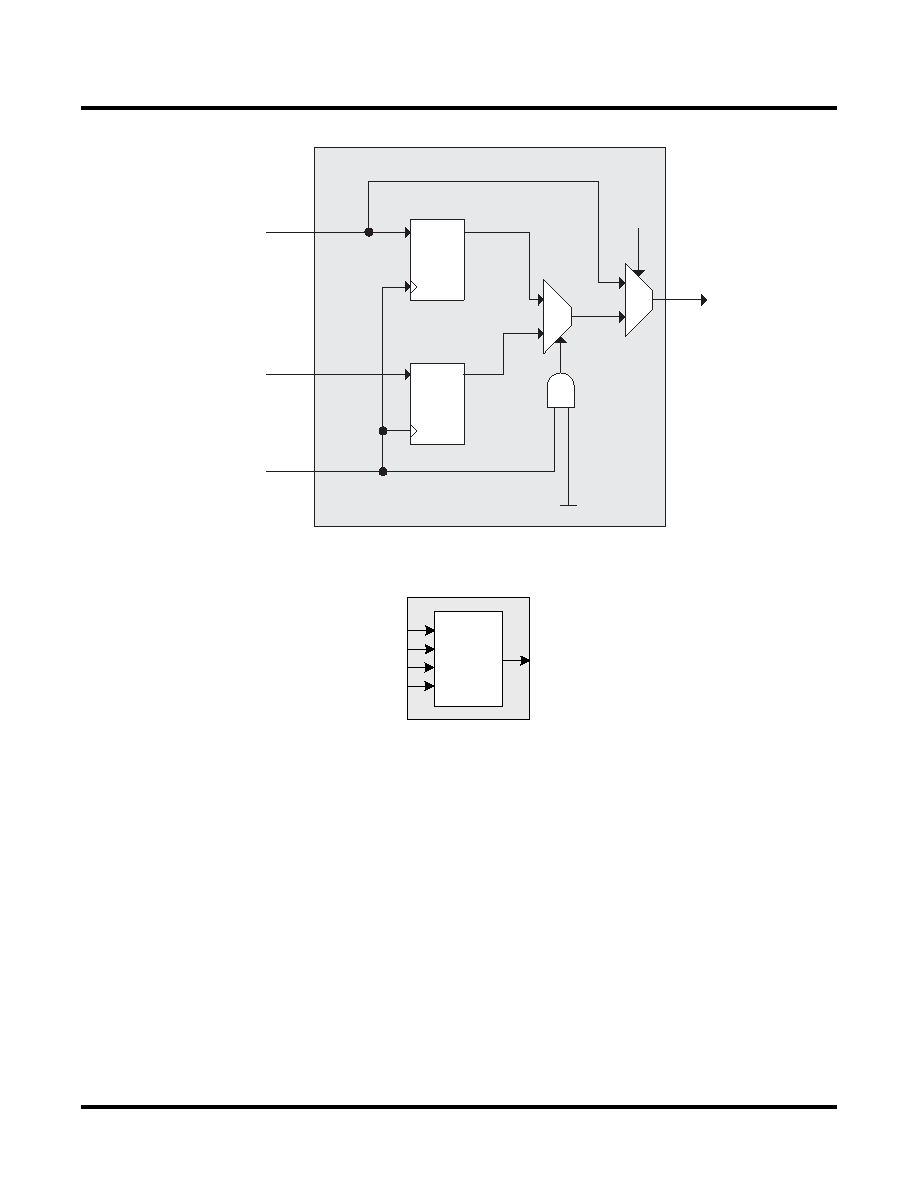

Figure 2-23. Output Register Block

Figure 2-24. ODDRXB Primitive

Tristate Register Block

The tristate register block provides the ability to register tri-state control signals from the core of the device before

they are passed to the sysIO buffers. The block contains a register for SDR operation and an additional latch for

DDR operation. Figure 2-25 shows the diagram of the Tristate Register Block.

In SDR mode, ONEG1 feeds one of the flip-flops that then feeds the output. The flip-flop can be configured a D-

type or latch. In DDR mode, ONEG1 is fed into one register on the positive edge of the clock and OPOS1 is

latched. A multiplexer running off the same clock selects the correct register for feeding to the output (D0).

D

Q

D

Q

D-Type

ONEG0

From

Routing

CLK1

*Latch is transparent when input is low.

Programmed

Control

DO

OPOS0

OUTDDN

/LATCH

LATCH

LE*

0

1

0

1

To sysIO

Buffer

ODDRXB

LSR

Q

DB

CLK

DA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LFXP15C-4FN256C | |

| LFZ3508VXX | GENERAL PURPOSE INDUCTOR |

| LFZ2805HXX | GENERAL PURPOSE INDUCTOR |

| LF02004VTX | GENERAL PURPOSE INDUCTOR |

| LG3341-NE7501 | T-1 SINGLE COLOR LED, GREEN, 3 mm |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LFXP217E5CF484C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:LatticeXP2 Family Data Sheet |

| LFXP217E5CF484I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:LatticeXP2 Family Data Sheet |

| LFXP217E5CF672C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:LatticeXP2 Family Data Sheet |

| LFXP217E5CF672I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:LatticeXP2 Family Data Sheet |

| LFXP217E5CFN484C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:LatticeXP2 Family Data Sheet |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。