- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384545 > ISPPAC-CLK5620V-01T100I (LATTICE SEMICONDUCTOR CORP) In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer PDF資料下載

參數(shù)資料

| 型號: | ISPPAC-CLK5620V-01T100I |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | 時鐘及定時 |

| 英文描述: | In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer |

| 中文描述: | 5600 SERIES, PLL BASED CLOCK DRIVER, 20 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP100 |

| 封裝: | TQFP-100 |

| 文件頁數(shù): | 27/47頁 |

| 文件大小: | 871K |

| 代理商: | ISPPAC-CLK5620V-01T100I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

Lattice Semiconductor

ispClock5600 Family Data Sheet

27

sumption by turning off unused drivers, these features can also be used for functional testing purposes. The follow-

ing inputs pins are used for output enable functions:

GOE – global output enable

OEX, OEY – secondary output enable controls

SGATE

– synchronous output control

Additionally, internal E

2

CMOS con

fi

guration bits are provided for the purpose of modifying the effects of these

external control pins.

When GOE is HIGH, all output drivers are forced into a high-Z state, regardless of any internal con

fi

guration. When

GOE is LOW, the output drivers may also be enabled or disabled on an individual basis, and optionally controlled

by the OEX and OEY pins. Internal E

2

CMOS con

fi

guration is used to establish whether the output driver is always

enabled (when GOE pin is LOW), never enabled (permanently off), or selectively enabled by the state of either

OEX or OEY. Bringing GOE high will also disable the internal feedback driver and will result in a loss of lock.

Synchronous output gating is provided by ispClock5600 devices through the use of the

SGATE

pin. The

SGATE

pin

does not disable the output driver, but merely forces the output to either a high or low state, depending on the out-

put driver’s polarity setting. If the output driver polarity is true, the output will be forced LOW when

SGATE

is

brought LOW, while if it is inverted, the output will be forced HIGH. A primary feature of the

SGATE

function is that

the clock output is enabled and disabled synchronous to the selected internal clock source. This prevents the gen-

eration of partial, ‘runt’, output clock pulses, which would otherwise occur with simple combinatorial gating

schemes. The

SGATE

is available to all clock outputs and is selectable on a bank-by-bank basis.

Table 5 shows the behavior of the outputs for various combinations of the output enables,

SGATE

input, and

E

2

CMOS con

fi

guration.

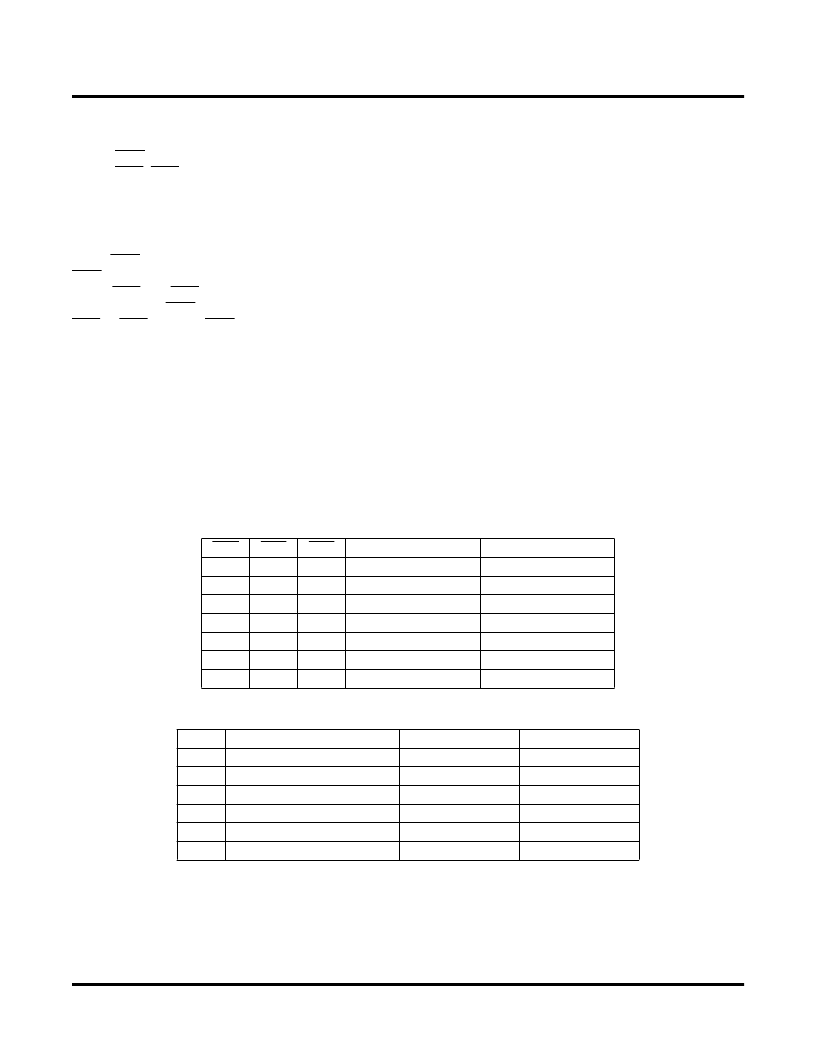

Table 5. Clock Output Enable Functions

Table 6. SGATE Function

Skew Control Units

Each of the ispClock5600’s clock outputs is supported by a skew control unit which allows the user to insert an indi-

vidually programmable delay into each output signal. This feature is useful when it is necessary to de-skew clock

signals to compensate for physical length variations among different PCB clock paths.

GOE

OEX

OEY

E

2

Con

fi

guration

Output

X

X

X

Always OFF

High-Z

0

X

X

Always ON

Clock Out

0

0

X

Enable on OEX

Clock Out

0

1

X

Enable on OEX

High-Z

0

X

0

Enable on OEY

Clock Out

0

X

1

Enable on OEY

High-Z

1

X

X

n/a

High-Z

SGATE Bank Controlled by SGATE

Output Polarity

Output

X

NO

True

Clock

X

NO

Inverted

Inverted Clock

0

YES

True

LOW

0

YES

Inverted

HIGH

1

YES

True

Clock

1

YES

Inverted

Inverted Clock

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISPPAC-CLK5610V-01T48C | Spot Light; LED Color:Blue; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No; Supply Current:160mA; Supply Voltage:30VDC; Wavelength:470nm |

| ISPPAC-CLK5620V-01T48C | LED Area Light; LED Color:Green; Leaded Process Compatible:No; Light Emitting Area:62x62mm; Peak Reflow Compatible (260 C):No; Supply Current:200mA; Supply Voltage:24VDC; Wavelength:525nm |

| ISPPAC-CLK5610V-01T48I | LED Area Light; LED Color:Green; Leaded Process Compatible:No; Light Emitting Area:80x80mm; Peak Reflow Compatible (260 C):No; Supply Current:250mA; Supply Voltage:24VDC; Wavelength:525nm |

| ISPPAC-CLK5620V-01T48I | Linear Array Light; LED Color:Green; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No; Supply Current:800mA; Supply Voltage:24VDC; Wavelength:530nm |

| ISPPAC-CLK5610V-01TN100C | LED On-Axis Light; LED Color:Green; Leaded Process Compatible:No; Light Emitting Area:100x100mm; Peak Reflow Compatible (260 C):No; Supply Current:500mA; Supply Voltage:24VDC; Wavelength:520nm |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISPPAC-CLK5620V-01T48C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer |

| ISPPAC-CLK5620V-01T48I | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer |

| ISPPAC-CLK5620V-01TN100C | 功能描述:時鐘驅(qū)動器及分配 PROGRAMMABLE ZERO DELAY CL GEN RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| ISPPAC-CLK5620V-01TN100I | 功能描述:時鐘驅(qū)動器及分配 PROGRAMMABLE ZERO DELAY CL GEN RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| ISPPAC-CLK5620V-01TN48C | 制造商:LATTICE 制造商全稱:Lattice Semiconductor 功能描述:In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。