- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄1924 > IDT88P8344BHI (IDT, Integrated Device Technology Inc)IC SPI3-SPI4 EXCHANGE 820-PBGA PDF資料下載

參數(shù)資料

| 型號(hào): | IDT88P8344BHI |

| 廠商: | IDT, Integrated Device Technology Inc |

| 文件頁(yè)數(shù): | 54/98頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC SPI3-SPI4 EXCHANGE 820-PBGA |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | * |

| 其它名稱(chēng): | 88P8344BHI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)當(dāng)前第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)

58

IDT88P8344 SPI EXCHANGE 4 x SPI-3 TO SPI-4

INDUSTRIALTEMPERATURERANGE

APRIL 10, 2006

EVEN_PARITY A SPI-3 interface is provisioned to generate and to check

for odd or even parity. The PARITY_EN bit must be set for this to become

effective. Odd parity is standard for SPI-3 interfaces.

0=Odd parity on this port

1=Even parity on this port

PARITY_EN A SPI-3 interface is provisioned to enable or disable parity

generation and checking, according to the state of the EVEN_PARITY bit.

0=Disable parity on this SPI-3 port

1=Enable parity on this SPI-3 port

WATERMARK

A SPI-3 interface can be set to a SPI-3 ingress port

watermark value. 0x10 is the highest watermark that can be set, meaning all

ingressbufferswillbefullbeforebackpressurewillbeinitiatedonaSPI-3ingress

interface. The WATERMARK field value of 0x08 is used to set the watermark

forahalf-fullingressbufferbeforetrippingbackpressure.TheunitsofWATER-

MARK are one-sixteenth of the available ingress buffering per unit. Each unit

isequalto128bytes. BACKPRESSURE_ENmustbeset [Register_offset0x01]

forthewatermarktobecomeeffective.Thewatermarkfieldisusuallysetto0x10,

andtheFREE_SEGMENTfieldofTable75,SPI-3ingressportdescriptortables

(Block_base 0x1200) is used for per LID backpressure.

SPI-3 ingress configuration register (Block_base

0x0200 + Register_offset 0x01)

There is one register for SPI-3 ingress configuration per SPI-3 interface.

Each register has read and write access.

The bit fields for a SPI-3 ingress configuration register are described in the

following paragraphs.

BACKPRESSURE_EN

A SPI-3 interface can have backpressure

enabled or disabled. Disabling backpressure means that data coming into the

ingress may be lost if the SPI-3 interface ingress buffers overflow. The SPI-3

interface can run at full-rate, however, since there will be no backpressure.

Attached devices that do not respond properly to backpressure should be

interfaced by disabling backpressure.

Enabling backpressure will cause the I_ENB signal to be asserted when the

ingressbufferfilllevelisequaltotheWATERMARKvalue[Register_offset0x00],

orthefreesegmentbufferthresholdTable75,SPI-3ingressportdescriptortable

(Block_base 0x1200) has been reached for any active LID.

0=Disable backpressure on this SPI-3 ingress.

1=Enable backpressure on this SPI-3 ingress interface.

FIX_LP

A SPI-3 interface can fix the logical port address to 0x00. This

is useful when there is only one LP on an interface, such as with some single-

PHY devices.

0=Donotfixlogicalportaddressto0x00,butusetheactual

LP found in the packet fragments.

1= Fix logical port address to 0x00

SPI-3 ingress fill level register (Block_base 0x0200

+ Register_offset 0x02)

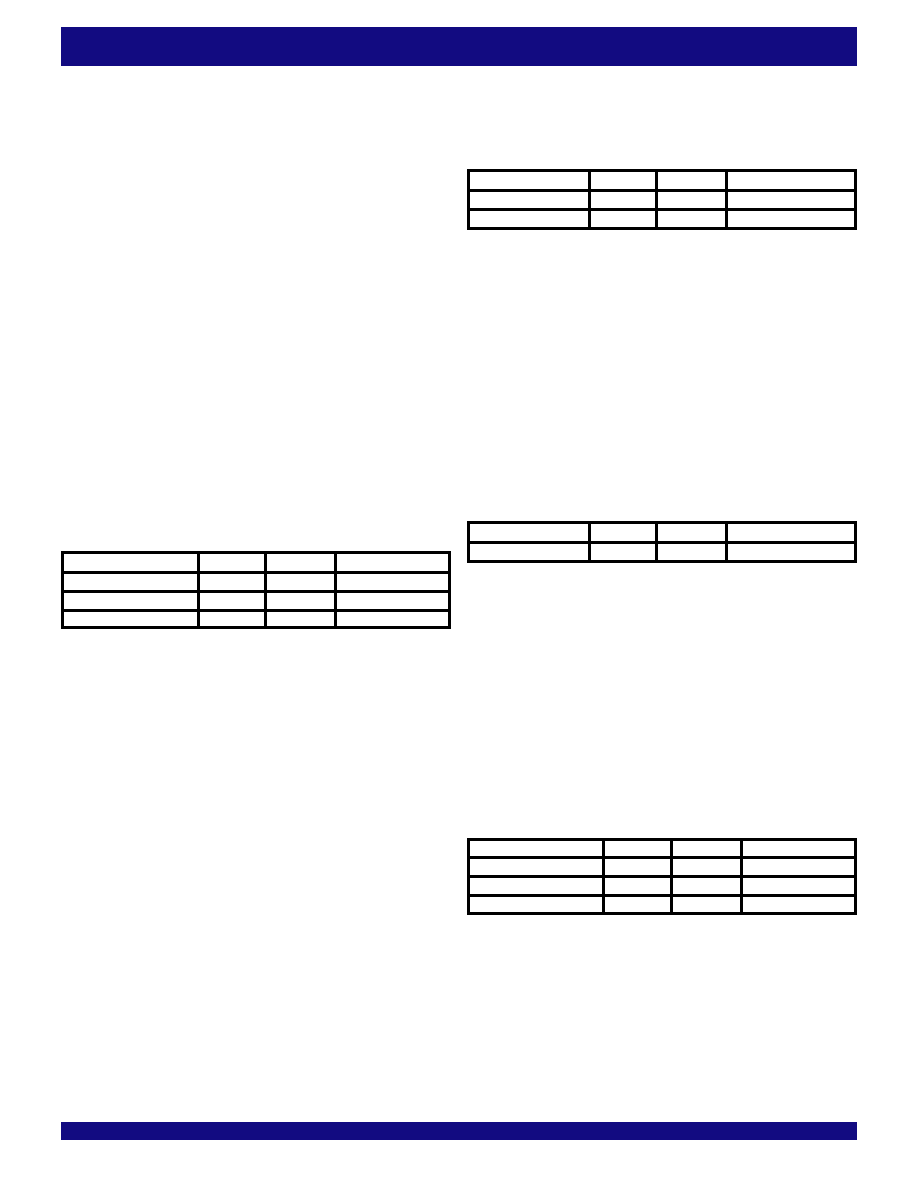

TABLE 51 - SPI-3 INGRESS CONFIGURATION

REGISTER(REGISTER_OFFSET=0x01)

Field

Bits

Length

Initial Value

BACKPRESSURE_EN

0

1

0b1

FIX_LP

1

0b0

Reserved

31:2

30

0x0000

There is one register for SPI-3 ingress fill level register per SPI-3 interface.

Each register has read-only access. The bit fields of a SPI-3 ingress fill level

register are described.

FILL_CUR

CurrentSPI-3ingressbufferfilllevel.Sincethisisareal-time

register, the value read from it will change rapidly and is used for internal

diagnosticsonly.

I_FCLK_AV Current SPI-3 ingress clock availability is checked here.

0=SPI-3 ingress clock not detected on a SPI-3 port

1=SPI-3ingressclocktransitionsdetectedonaSPI-3port

SPI-3 ingress max fill register (Block_base 0x0200

+ Register_offset 0x03)

TABLE 52 - SPI-3 INGRESS FILL LEVEL REGISTER

(REGISTER_OFFSET=0x02)

Field

Bits

Length

Initial Value

FILL_CUR

4:0

5

0x00

I_FCLK_AV

5

1

0b1

TABLE 53 - SPI-3 INGRESS MAX FILL LEVEL

REGISTER(REGISTER_OFFSET=0x03)

Field

Bits

Length

Initial Value

FILL_MAX

4:0

5

0x00

There is one register for SPI-3 ingress max fill level register per SPI-3

interface. Each register has read-only access, and is cleared after reading.

0x10isthehighestfillinglevel,meaningallingressbuffershadbeenfullatsome

time since the last read of the FILL_MAX field. The units of FILL_MAX are one-

sixteenthoftheavailableingressbuffering.Eachunitisequalto128bytes.The

bitfieldofaSPI-3ingressmaxfilllevelregisterisdescribed.TheTable53-SPI-

3 ingress max fill level register (Register_offset=0x03) is for diagnostics only.

FILL_MAX

Maximum SPI-3 ingress buffer fill level since the last read of

the SPI-3 ingress max fill level register.

9.3.3 Block base 0x0500 registers

SPI-3 egress LID to LP map (Block_base 0x0500 +

Register_offset 0x00-0x3F)

TABLE 54 - SPI-3 EGRESS LID TO LP MAP

Field

Bits

Length

Initial Value

LP

7:0

8

0x00

ENABLE

8

1

0b0

BIT_REVERSAL

9

1

0b0

There are 64 SPI-3 egress LID to LP maps per SPI-3 interface, one per

potential SPI-3 LID.

The SPI-3 egress LID to LP maps have read and write access. The SPI-

3egressLIDtoLPmapsareusedtomapSPI-3egresslogicalidentifierstoSPI-

3logicalportaddressesthatarein-bandwiththeSPI-3egresspacketfragments.

LP

The LP programmed is associated to the LID with the same number

as the register address.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT89H24NT24G2ZBHLG | IC PCI SW 24LANE 24PORT 324BGA |

| IDT89HPES16NT2ZBBCG | IC PCI SW 16LANE 2PORT 484-CABGA |

| IDT89HPES24NT3ZBBXG | IC PCI SW 24LANE 3PORT 420-SBGA |

| IDT89HPES32T8ZHBXG | IC PCI SW 32LANE 8PORT 500-SBGA |

| IDT89HPES8NT2ZBBCG | IC PCI SW 8LANE 2PORT 324-CABGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT89H10T4BG2ZBBC | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

| IDT89H10T4BG2ZBBC8 | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

| IDT89H10T4BG2ZBBCG | 功能描述:IC PCI SW 10LANE 4PORT 324BGA RoHS:是 類(lèi)別:集成電路 (IC) >> 專(zhuān)用 IC 系列:PRECISE™ 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:1 系列:- 類(lèi)型:調(diào)幀器 應(yīng)用:數(shù)據(jù)傳輸 安裝類(lèi)型:表面貼裝 封裝/外殼:400-BBGA 供應(yīng)商設(shè)備封裝:400-PBGA(27x27) 包裝:散裝 |

| IDT89H10T4BG2ZBBCG8 | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

| IDT89H10T4BG2ZBBCGI | 制造商:Integrated Device Technology Inc 功能描述:IC PCI SW 10LANE 4PORT 324BGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。