- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299200 > IDT7005L55FB (INTEGRATED DEVICE TECHNOLOGY INC) Single, Ultra Low Cost, RRIO CMOS Amplifier PDF資料下載

參數(shù)資料

| 型號: | IDT7005L55FB |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | SRAM |

| 英文描述: | Single, Ultra Low Cost, RRIO CMOS Amplifier |

| 中文描述: | 8K X 8 DUAL-PORT SRAM, 55 ns, QFP68 |

| 封裝: | 0.970 X 0.970 INCH, 0.080 INCH HEIGHT, QFP-68 |

| 文件頁數(shù): | 8/20頁 |

| 文件大?。?/td> | 189K |

| 代理商: | IDT7005L55FB |

6.42

IDT7005S/L

High-Speed 8K x 8 Dual-Port Static RAM

Military, Industrial and Commercial Temperature Ranges

16

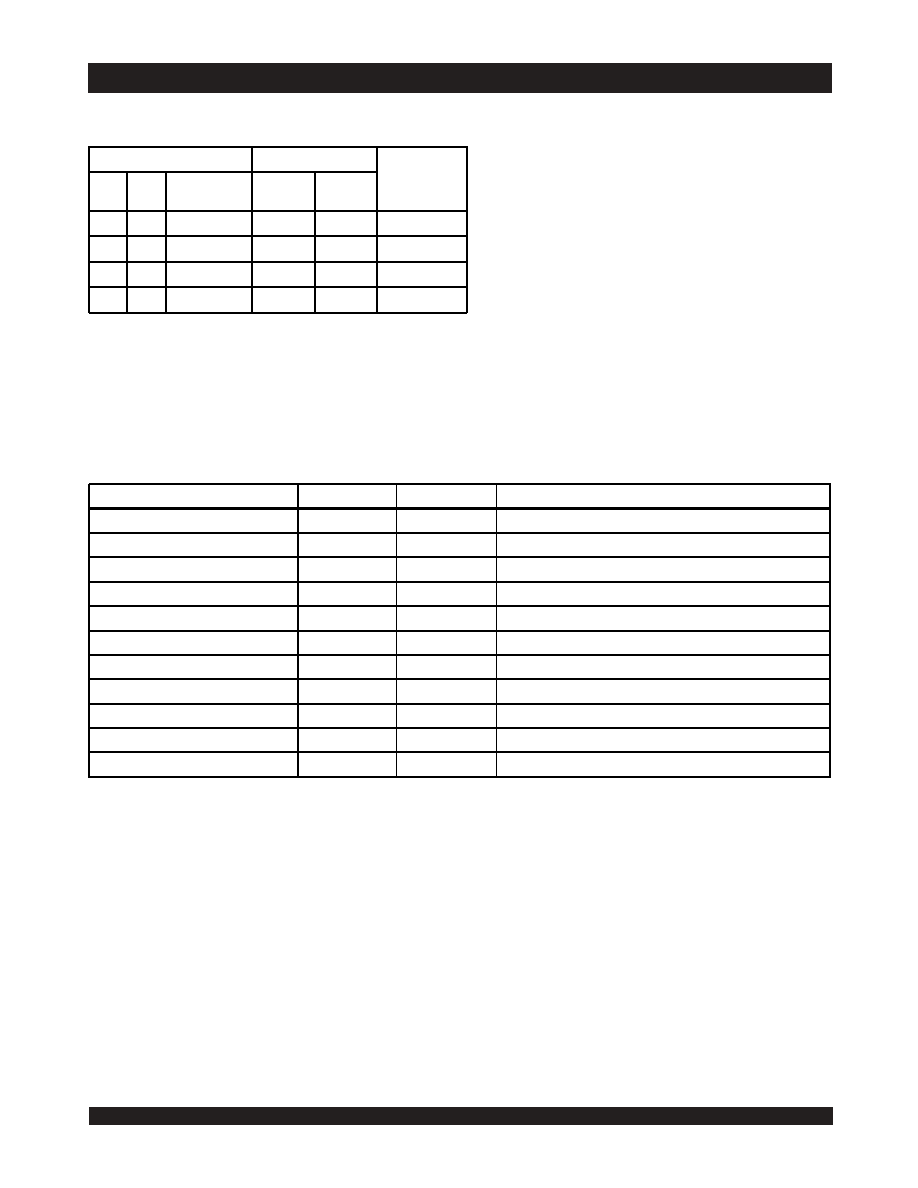

Truth Table IV — Address BUSY

Arbitration

NOTES:

1. Pins

BUSYL and BUSYR are both outputs when the part is configured as a master. Both are inputs when configured as a slave. BUSYX outputs on the IDT7005 are

push-pull, not open drain outputs. On slaves the

BUSYX input internally inhibits writes.

2. 'L' if the inputs to the opposite port were stable prior to the address and enable inputs of this port. 'H' if the inputs to the opposite port became stable after the address

and enable inputs of this port. If tAPS is not met, either

BUSYL or BUSYR = LOW will result. BUSYL and BUSYR outputs can not be LOW simultaneously.

3. Writes to the left port are internally ignored when

BUSYL outputs are driving LOW regardless of actual logic level on the pin. Writes to the right port are internally ignored

when

BUSYR outputs are driving LOW regardless of actual logic level on the pin.

Truth Table V — Example of Semaphore Procurement Sequence(1,2,3)

Functional Description

The IDT7005 provides two ports with separate control, address and

I/Opinsthatpermitindependentaccessforreadsorwritestoanylocation

inmemory.TheIDT7005hasanautomaticpowerdownfeaturecontrolled

by

CE. The CE controls on-chip power down circuitry that permits the

respective port to go into a standby mode when not selected (

CE HIGH).

When a port is enabled, access to the entire memory array is permitted.

Interrupts

Iftheuserchoosestheinterruptfunction,amemorylocation(mailbox

or message center) is assigned to each port. The left port interrupt flag

(

INTL) is asserted when the right port writes to memory location 1FFE

(HEX), where a write is defined as

CE = R/W= VIL per Truth Table III.

The left port clears the interrupt through access of address location 1FFE

when

CE = OE = VIL. For this example, R/W is a "don't care". Likewise,

the right port interrupt flag (INTR) is asserted when the left port writes to

memory location 1FFF (HEX) and to clear the interrupt flag (INTR), the

right port must read the memory location 1FFF. The message (8 bits) at

1FFE or 1FFF is user-defined, since it is an addressable SRAM location.

If the interrupt function is not used, address locations 1FFE and 1FFF are

not used as mail boxes, but as part of the random access memory. Refer

to Truth Table III for the interrupt operation.

NOTES:

1. This table denotes a sequence of events for only one of the eight semaphores on the IDT7005.

2. There are eight semaphore flags written to via I/O0 and read from all I/O's. These eight semaphores are addressed by A0 - A2.

3.

CE=VIH, SEM=VIL to access the semaphores. Refer to the semaphore Read/Write Control Truth Table.

Inputs

Outputs

Function

CEL

CER

AOL-A12L

AOR-A12R

BUSYL(1)

BUSYR(1)

X

NO MATCH

H

Normal

H

X

MATCH

HHNormal

X

H

MATCH

HHNormal

L

MATCH

(2)

Write Inhibit

(3)

2738 tbl 18

Functions

D0 - D7 Left

D0 - D7 Right

Status

No Action

1

Semaphore free

Left Port Writes "0" to Semaphore

0

1

Left port has semaphore token

Rig ht Port Writes "0" to Semaphore

0

1

No change. Right side has no write access to semaphore

Left Port Writes "1" to Semaphore

1

0

Right port obtains semaphore token

Left Port Writes "0" to Semaphore

1

0

No change. Left port has no write access to semaphore

Rig ht Port Writes "1" to Semaphore

0

1

Left port obtains semaphore token

Left Port Writes "1" to Semaphore

1

Semaphore free

Rig ht Port Writes "0" to Semaphore

1

0

Right port has semaphore token

Rig ht Port Writes "1" to Semaphore

1

Semaphore free

Left Port Writes "0" to Semaphore

0

1

Left port has semaphore token

Left Port Writes "1" to Semaphore

1

Semaphore free

2738 tbl 19

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT7005L55G | Single, Ultra Low Cost, RRIO CMOS Amplifier; Package: SOT-23; No of Pins: 5; Container: Tape & Reel |

| IDT7005L55GB | Single, Ultra Low Cost, RRIO CMOS Amplifier |

| IDT7005L55J | Dual, Ultra Low Cost, RRIO CMOS Amplifier; Package: MSOP; No of Pins: 8; Container: Tape & Reel |

| IDT7005L55PF | Dual, Ultra Low Cost, RRIO CMOS Amplifier |

| IDT7005L55PFB | HIGH-SPEED 8K x 8 DUAL-PORT STATIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT7005L55G | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:HIGH-SPEED 8K x 8 DUAL-PORT STATIC RAM |

| IDT7005L55GB | 制造商:Integrated Device Technology Inc 功能描述:IC SRAM 64KBIT 55NS 68PGA |

| IDT7005L55J | 功能描述:IC SRAM 64KBIT 55NS 68PLCC RoHS:否 類別:集成電路 (IC) >> 存儲器 系列:- 標準包裝:45 系列:- 格式 - 存儲器:RAM 存儲器類型:SRAM - 雙端口,異步 存儲容量:128K(8K x 16) 速度:15ns 接口:并聯(lián) 電源電壓:3 V ~ 3.6 V 工作溫度:0°C ~ 70°C 封裝/外殼:100-LQFP 供應商設(shè)備封裝:100-TQFP(14x14) 包裝:托盤 其它名稱:70V25S15PF |

| IDT7005L55J8 | 功能描述:IC SRAM 64KBIT 55NS 68PLCC RoHS:否 類別:集成電路 (IC) >> 存儲器 系列:- 標準包裝:72 系列:- 格式 - 存儲器:RAM 存儲器類型:SRAM - 同步 存儲容量:9M(256K x 36) 速度:75ns 接口:并聯(lián) 電源電壓:3.135 V ~ 3.465 V 工作溫度:-40°C ~ 85°C 封裝/外殼:100-LQFP 供應商設(shè)備封裝:100-TQFP(14x14) 包裝:托盤 其它名稱:71V67703S75PFGI |

| IDT7005L55JB | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:HIGH-SPEED 8K x 8 DUAL-PORT STATIC RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。