- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄223993 > HY5PS1G831ALFP-C4 (HYNIX SEMICONDUCTOR INC) 128M X 8 DDR DRAM, PBGA68 PDF資料下載

參數(shù)資料

| 型號(hào): | HY5PS1G831ALFP-C4 |

| 廠商: | HYNIX SEMICONDUCTOR INC |

| 元件分類: | DRAM |

| 英文描述: | 128M X 8 DDR DRAM, PBGA68 |

| 封裝: | FBGA-68 |

| 文件頁(yè)數(shù): | 16/36頁(yè) |

| 文件大小: | 574K |

| 代理商: | HY5PS1G831ALFP-C4 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

Rev. 0.7 / Oct. 2007

23

HY5PS1G431A(L)FP

HY5PS1G831A(L)FP

HY5PS1G1631A(L)FP

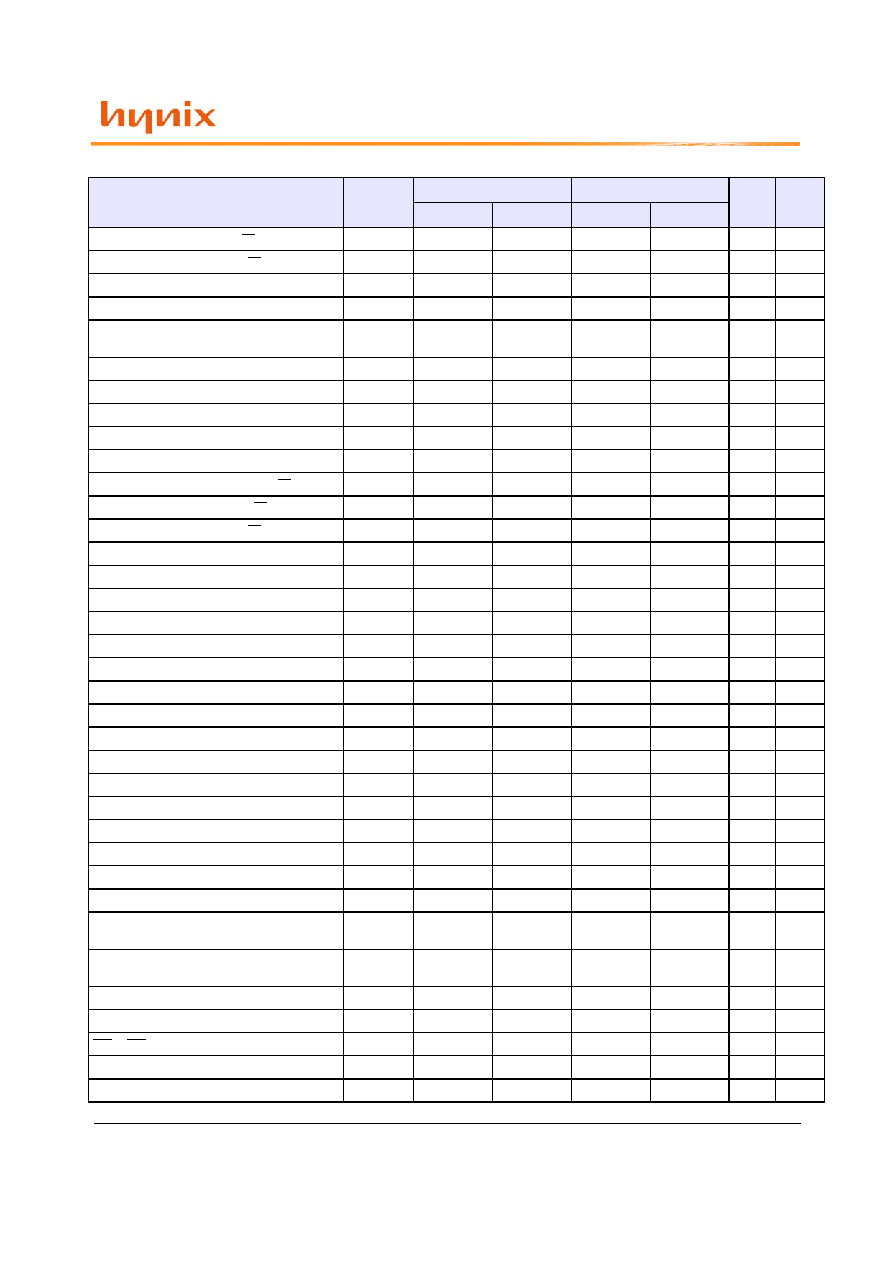

Parameter

Symbol

DDR2-667

DDR2-800

Unit

Note

min

max

min

max

DQ output access time from CK/CK

tAC

-450

+450

-400

+400

ps

DQS output access time from CK/CK

tDQSCK

-400

+400

-350

+350

ps

CK high-level width

tCH

0.45

0.55

0.45

0.55

tCK

CK low-level width

tCL

0.45

0.55

0.45

0.55

tCK

CK half period

tHP

min(tCL,

tCH)

-

min(tCL,

tCH)

-

ps

11,12

Clock cycle time, CL=x

tCK

3000

8000

2500

ps

15

DQ and DM input setup time

tDS(base)

100

-

50

-

ps

6,7,8,20

DQ and DM input hold time

tDH(base)

175

-

125

-

ps

6,7,8,21

Control & Address input pulse width for each input

tIPW

0.6

-

0.6

-

tCK

DQ and DM input pulse width for each input

tDIPW

0.35

-

0.35

-

tCK

Data-out high-impedance time from CK/CK

tHZ

-

tAC max

-

tAC max

ps

18

DQS low-impedance time from CK/CK

tLZ(DQS)

tAC min

tAC max

tAC min

tAC max

ps

18

DQ low-impedance time from CK/CK

tLZ(DQ)

2*tAC min

tAC max

2*tAC min

tAC max

ps

18

DQS-DQ skew for DQS and associated DQ signals

tDQSQ

-

240

-200

ps

13

DQ hold skew factor

tQHS

-

340

-300

ps

12

DQ/DQS output hold time from DQS

tQH

tHP - tQHS

-

tHP - tQHS

-

ps

First DQS latching transition to associated clock edge tDQSS

- 0.25

+ 0.25

- 0.25

+ 0.25

tCK

DQS input high pulse width

tDQSH

0.35

-

0.35

-

tCK

DQS input low pulse width

tDQSL

0.35

-

0.35

-

tCK

DQS falling edge to CK setup time

tDSS

0.2

-

0.2

-

tCK

DQS falling edge hold time from CK

tDSH

0.2

-

0.2

-

tCK

Mode register set command cycle time

tMRD

2

-

2

-

tCK

Write postamble

tWPST

0.4

0.6

0.4

0.6

tCK

10

Write preamble

tWPRE

0.35

-

0.35

-

tCK

Address and control input setup time

tIS(base)

200

-175

-

ps

5,7,9,22

Address and control input hold time

tIH(base)

275

-250

-

ps

5,7,9,23

Read preamble

tRPRE

0.9

1.1

0.9

1.1

tCK

19

Read postamble

tRPST

0.4

0.6

0.4

0.6

tCK

19

Activate to precharge command

tRAS

45

70000

45

70000

ns

3

Active to active command period for 1KB page size

products

tRRD

7.5

-7.5

-

ns

4

Active to active command period for 2KB page size

products

tRRD

10

-10

-

ns

4

Four Active Window for 1KB page size products

tFAW

37.5

-

37.5

-

ns

Four Active Window for 2KB page size products

tFAW

50

-

50

-

ns

CAS to CAS command delay

tCCD

2

tCK

Write recovery time

tWR

15

-15

-

ns

Auto precharge write recovery + precharge time

tDAL

WR+tRP

-

WR+tRP

-

tCK

14

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HY5PS1G831ALFP-Y5 | 128M X 8 DDR DRAM, PBGA68 |

| HY5RS573225AFP-16L | 8M X 32 DDR DRAM, 0.28 ns, PBGA136 |

| HY5V28CF-S | 16M X 8 SYNCHRONOUS DRAM, 6 ns, PBGA54 |

| HY5V28CLF-S | 16M X 8 SYNCHRONOUS DRAM, 6 ns, PBGA54 |

| HY5V52CLF-6 | 8M X 32 SYNCHRONOUS DRAM, 5.4 ns, PBGA90 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HY5PS1G831CFP | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:1Gb DDR2 SDRAM |

| HY5PS1G831CFP-C4 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:1Gb DDR2 SDRAM |

| HY5PS1G831CFP-E3 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:1Gb DDR2 SDRAM |

| HY5PS1G831CFP-S5 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:1Gb DDR2 SDRAM |

| HY5PS1G831CFP-Y5 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:1Gb DDR2 SDRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。