- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371797 > HDMP-2634 1.25 and 2.5 Gbps SerDes Circuits PDF資料下載

參數(shù)資料

| 型號(hào): | HDMP-2634 |

| 英文描述: | 1.25 and 2.5 Gbps SerDes Circuits |

| 中文描述: | 1.25和2.5 Gbps的SerDes電路 |

| 文件頁(yè)數(shù): | 3/12頁(yè) |

| 文件大?。?/td> | 177K |

| 代理商: | HDMP-2634 |

3

Hard Disk

Connection to PBC Cells

CDR Position (x)

Cell Connected to Cable

A

1

xA

0

A

0

Ax

1

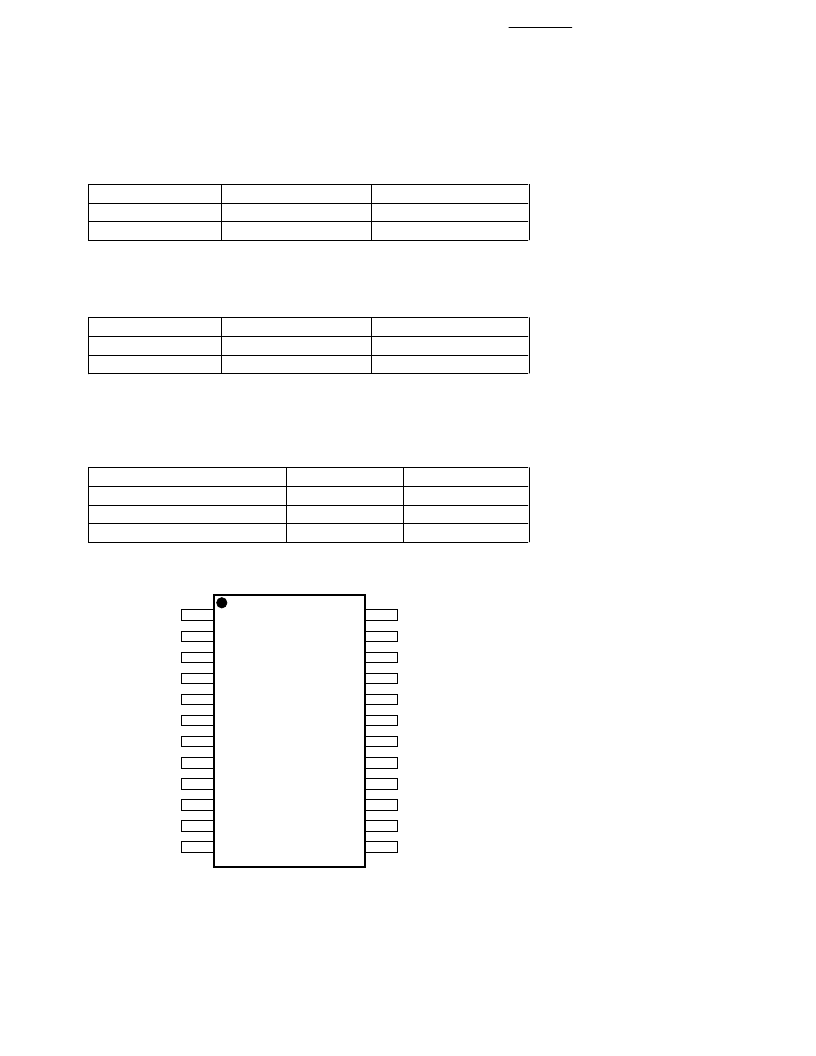

Figure 3: HDMP-0421 Package Layout and Marking, Top View.

TO_LOOP

FM_LOOP

FM_NODE[1]

TO_NODE[1]

FM_LOOP

FM_LOOP

BYPASS[1]–

0

1

Table 1a. Truth Table for CDR at Entry Configurations

FM_LOOP = FM_NODE[0], TO_LOOP = TO_NODE[0], BYPASS[0]– = 1

TO_LOOP

FM_LOOP

FM_NODE[0]

TO_NODE[0]

FM_LOOP

FM_LOOP

BYPASS[0]–

0

1

Table 1b. Truth Table for CDR at Exit Configurations

FM_LOOP = FM_NODE[1], TO_LOOP = TO_NODE[1], BYPASS[1]– = 1

Table 2. Pin Connection Diagram to Achieve Desired

CDR Location (see Figures 4 and 5)

X Denotes CDR Position with respect to Hard Disks

FM_NODE[1]–

FM_NODE[1]+

V

CC

HS

TO_NODE[1]–

TO_NODE[1]+

GND

GND

BYPASS[1]–

V

CC

SD[1]

GND

CPLL1

FM_NODE[0]–

FM_NODE[0]+

V

CC

HS

TO_NODE[0]–

TO_NODE[0]+

GND

GND

BYPASS[0]–

V

CC

A

SD[0]

REFCLK

CPLL0

24

23

22

21

20

19

18

17

15

16

14

13

1

2

3

4

5

6

7

8

10

9

11

12

HDMP-0421

R x.YY

nnnn-nnn

S YYWW

COUNTRY

nnnn.nnn = WAFER LOT - BUILD NUMBER (1-3 DIGITS)

Rx.yy = DIE REVISION

S = SUPPLIER CODE

YYWW = DATE CODE (YY = YEAR, WW = WORK WEEK)

COUNTRY = COUNTRY OF MANUFACTURE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HDMP-3001 | Telecommunication IC |

| HDMP-3001K | Evaluation Board for Multi-Protocol IC (MPIC) Ethernet Over SONET/SDH (EOS) Mapper |

| HDMP-3268 | 3.2 GBit/sec 68 x 68 Digital Crosspoint Switch |

| HDMP-0450 | Quad Port Bypass Circuit for Fibre Channel Arbitrated Loops |

| HDMP-0452 | Quad Port Bypass Circuit with CDR for Fibre Channel Arbitrated Loops |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HDMP-2689 | 制造商:Agilent Technologies 功能描述: |

| HDMP-2840 | 制造商:Rochester Electronics LLC 功能描述: 制造商:PMC-Sierra 功能描述: |

| HDMP-29-01-S-EM | 制造商:Samtec Inc 功能描述:HDMP INSULATOR FOR LOCKING PLUG - Bulk |

| HDMP-3001 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication IC |

| HDMP-3001K | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Evaluation Board for Multi-Protocol IC (MPIC) Ethernet Over SONET/SDH (EOS) Mapper |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。