- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97917 > EP20K200CP208I9ES ASIC PDF資料下載

參數(shù)資料

| 型號: | EP20K200CP208I9ES |

| 英文描述: | ASIC |

| 中文描述: | 專用集成電路 |

| 文件頁數(shù): | 79/114頁 |

| 文件大?。?/td> | 1623K |

| 代理商: | EP20K200CP208I9ES |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁當前第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁

Altera Corporation

67

APEX 20K Programmable Logic Device Family Data Sheet

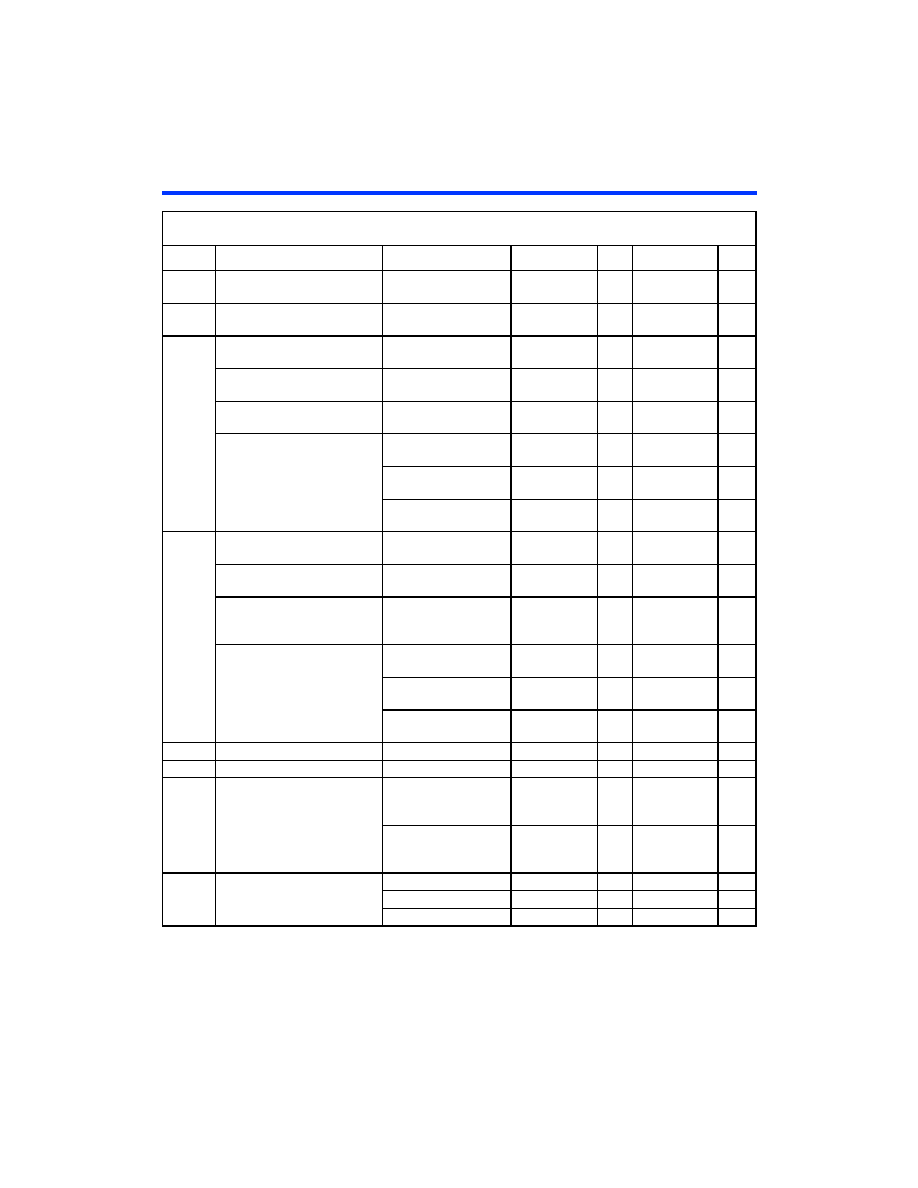

Table 33. APEX 20KE Device DC Operating Conditions

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

VIH

High-level LVTTL, CMOS, or 3.3-V

PCI input voltage

1.7, 0.5

× V

CCIO

4.1

V

VIL

Low-level LVTTL, CMOS, or 3.3-V

PCI input voltage

–0.5

0.8, 0.3

× V

CCIO

V

VOH

3.3-V high-level LVTTL output

voltage

IOH = –12 mA DC,

2.4

V

3.3-V high-level LVCMOS output

voltage

IOH = –0.1 mA DC,

VCCIO – 0.2

V

3.3-V high-level PCI output voltage IOH = –0.5 mA DC,

0.9

× V

CCIO

V

2.5-V high-level output voltage

IOH = –0.1 mA DC,

2.1

V

IOH = –1 mA DC,

2.0

V

IOH = –2 mA DC,

1.7

V

VOL

3.3-V low-level LVTTL output

voltage

IOL = 12 mA DC,

0.4

V

3.3-V low-level LVCMOS output

voltage

IOL = 0.1 mA DC,

0.2

V

3.3-V low-level PCI output voltage IOL = 1.5 mA DC,

VCCIO = 3.00 to 3.60 V

0.1

× V

CCIO

V

2.5-V low-level output voltage

IOL = 0.1 mA DC,

0.2

V

IOL = 1 mA DC,

0.4

V

IOL = 2 mA DC,

0.7

V

II

Input pin leakage current

–10

10

A

IOZ

Tri-stated I/O pin leakage current

–10

10

A

ICC0

VCC supply current (standby)

(All ESBs in power-down mode)

VI = ground, no load, no

toggling inputs, -1 speed

grade

10

mA

VI = ground, no load, no

toggling inputs,

-2, -3 speed grades

5mA

RCONF

Value of I/O pin pull-up resistor

before and during configuration

20

50

k

30

80

k

60

150

k

相關PDF資料 |

PDF描述 |

|---|---|

| EP20K200CP240C7 | ASIC |

| EP20K200CP240C7ES | ASIC |

| EP20K200CP240C8 | ASIC |

| EP20K200CP240C8ES | ASIC |

| EP20K200CP240C9 | ASIC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EP20K200CP240C7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EP20K200CP240C7ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EP20K200CP240C8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EP20K200CP240C8ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EP20K200CP240C9 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

發(fā)布緊急采購,3分鐘左右您將得到回復。