- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97917 > EP20K200CP208I9ES ASIC PDF資料下載

參數(shù)資料

| 型號(hào): | EP20K200CP208I9ES |

| 英文描述: | ASIC |

| 中文描述: | 專用集成電路 |

| 文件頁數(shù): | 57/114頁 |

| 文件大小: | 1623K |

| 代理商: | EP20K200CP208I9ES |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁當(dāng)前第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁

Altera Corporation

47

APEX 20K Programmable Logic Device Family Data Sheet

APEX 20KE devices also support the MultiVolt I/O interface feature. The

APEX 20KE VCCINT pins must always be connected to a 1.8-V power

supply. With a 1.8-V VCCINT level, input pins are 1.8-V, 2.5-V, and 3.3-V

tolerant. The VCCIO pins can be connected to either a 1.8-V, 2.5-V, or 3.3-V

power supply, depending on the I/O standard requirements. When the

VCCIO

pins are connected to a 1.8-V power supply, the output levels are

compatible with 1.8-V systems. When VCCIO pins are connected to a 2.5-V

power supply, the output levels are compatible with 2.5-V systems. When

VCCIO

pins are connected to a 3.3-V power supply, the output high is

3.3 V and compatible with 3.3-V or 5.0-V systems. An APEX 20KE device

is 5.0-V tolerant with the addition of a resistor.

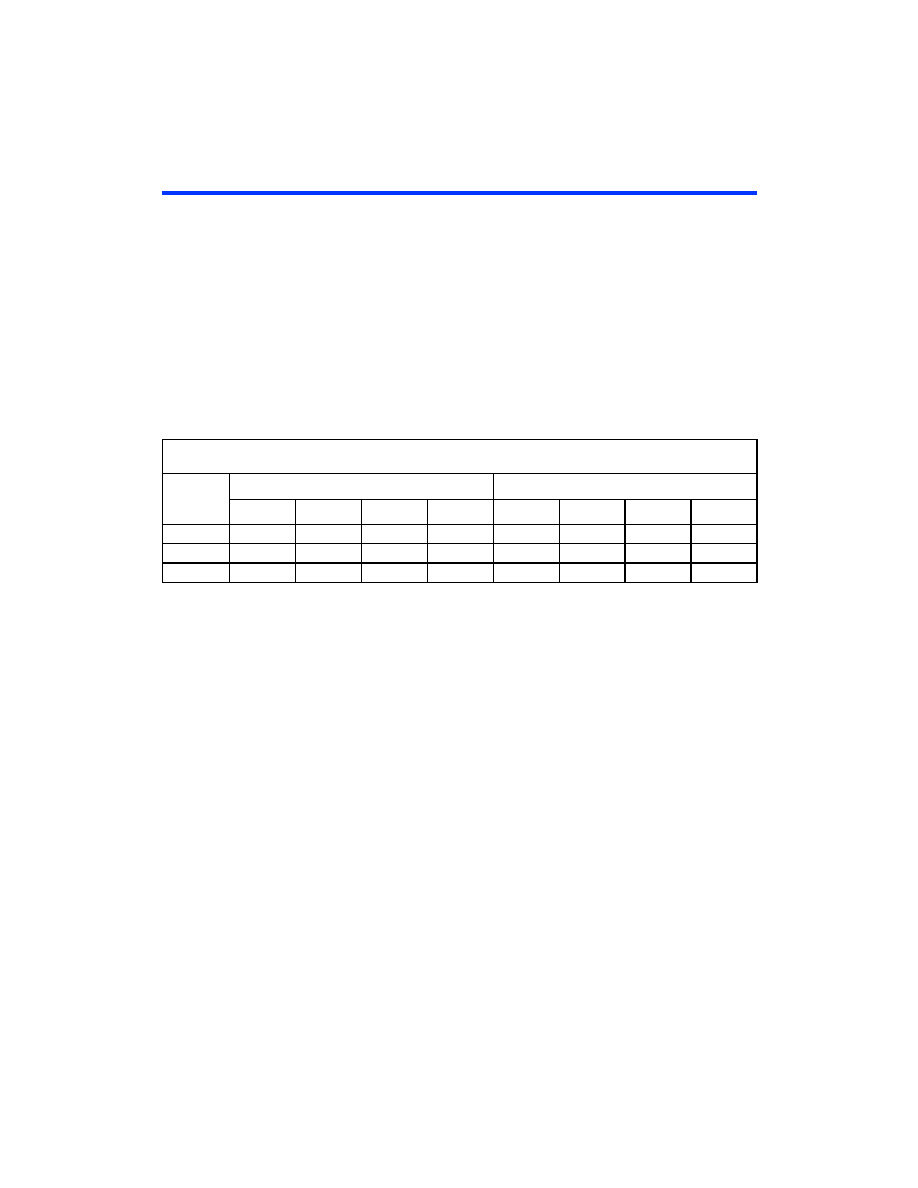

Table 13 summarizes APEX 20KE MultiVolt I/O support.

Notes:

(1)

The PCI clamping diode must be disabled to drive an input with voltages higher than VCCIO, except for the 5.0-V

input case.

(2)

An APEX 20KE device can be made 5.0-V tolerant with the addition of an external resistor.

(3)

When VCCIO = 3.3 V, an APEX 20KE device can drive a 2.5-V device with 3.3-V tolerant inputs.

ClockLock &

ClockBoost

Features

APEX 20K devices support the ClockLock and ClockBoost clock

management features, which are implemented with PLLs. The ClockLock

circuitry uses a synchronizing PLL that reduces the clock delay and skew

within a device. This reduction minimizes clock-to-output and setup

times while maintaining zero hold times. The ClockBoost circuitry, which

provides a clock multiplier, allows the designer to enhance device area

efficiency by sharing resources within the device. The ClockBoost

circuitry allows the designer to distribute a low-speed clock and multiply

that clock on-device. APEX 20K devices include a high-speed clock tree;

unlike ASICs, the user does not have to design and optimize the clock tree.

The ClockLock and ClockBoost features work in conjunction with the

APEX 20K device’s high-speed clock to provide significant improvements

in system performance and band-width. Devices with an X-suffix on the

ordering code include the ClockLock circuit.

The ClockLock and ClockBoost features in APEX 20K devices are enabled

through the Quartus II software. External devices are not required to use

these features.

Table 13. APEX 20KE MultiVolt I/O Support

VCCIO (V)

Input Signals (V)

Output Signals (V)

1.8

2.5

3.3

5.0

1.8

2.5

3.3

5.0

1.8

vv (1)

v

2.5

v

3.3

vv

v (2)

vv

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP20K200CP240C7 | ASIC |

| EP20K200CP240C7ES | ASIC |

| EP20K200CP240C8 | ASIC |

| EP20K200CP240C8ES | ASIC |

| EP20K200CP240C9 | ASIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP20K200CP240C7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EP20K200CP240C7ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EP20K200CP240C8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EP20K200CP240C8ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EP20K200CP240C9 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。