- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299019 > EBE41FE4ACFT-6E-E (ELPIDA MEMORY INC) 512M X 72 DDR DRAM MODULE, DMA240 PDF資料下載

參數(shù)資料

| 型號(hào): | EBE41FE4ACFT-6E-E |

| 廠商: | ELPIDA MEMORY INC |

| 元件分類: | DRAM |

| 英文描述: | 512M X 72 DDR DRAM MODULE, DMA240 |

| 封裝: | ROHS COMPLIANT, FBDIMM-240 |

| 文件頁數(shù): | 4/22頁 |

| 文件大?。?/td> | 205K |

| 代理商: | EBE41FE4ACFT-6E-E |

EBE41FE4ACFT

Data Sheet E1091E30 (Ver. 3.0)

12

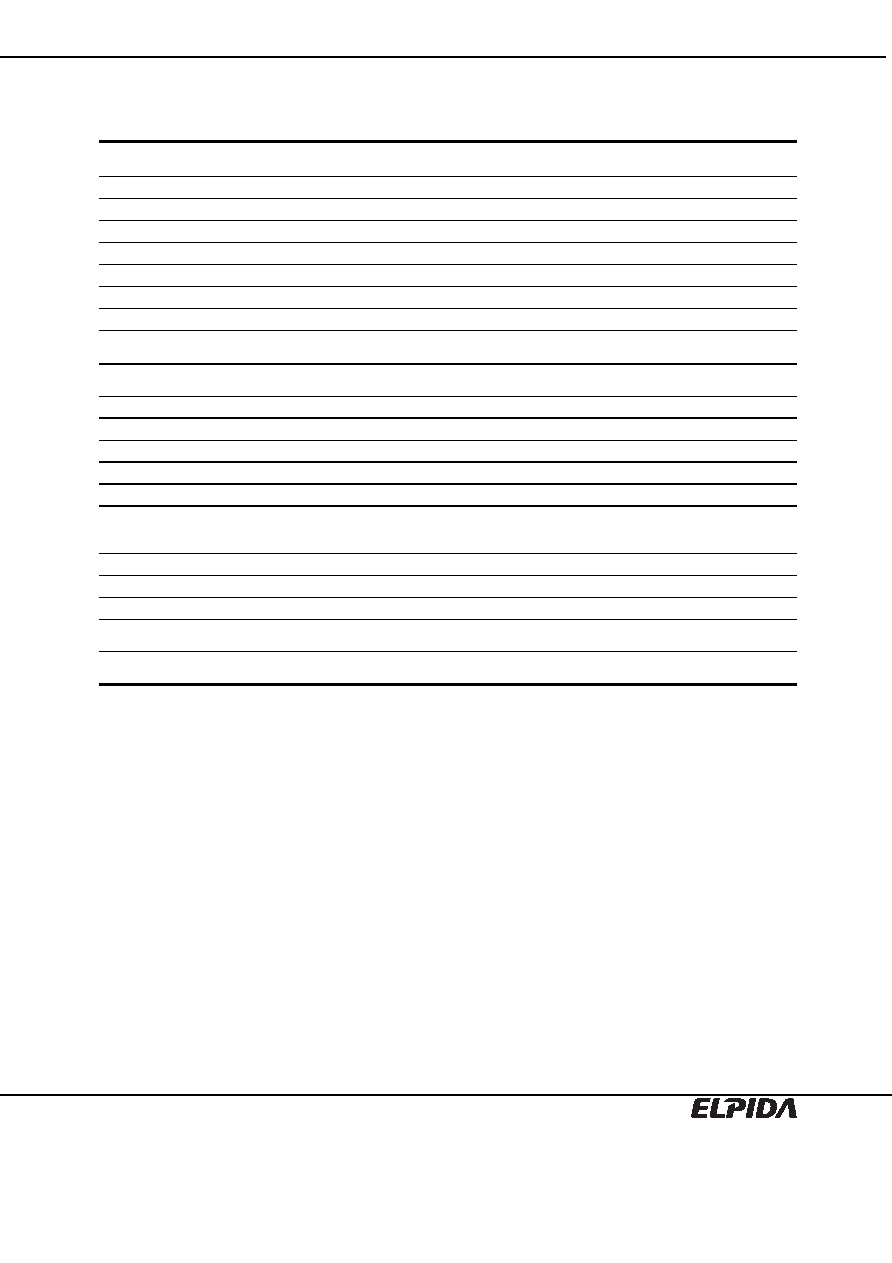

Reference Clock Input Specifications*

1

Parameter

Symbol

min.

max.

Units

Notes

Reference clock frequency@ 4.0 Gb/s

(nominal 166.67MHz)

fRefclk-4.0

158.33

166.75

MHz

2, 3, 4

Single-ended maximum voltage

Vmax

1.15

V

5, 7

Single-ended minimum voltage

Vmin

0.3

V

5, 8

Differential voltage high

VRefclk-diff-ih

150

mV

6

Differential voltage low

VRefclk-diff-il

150

mV

6

Absolute crossing point

VCross

250

550

mV

5, 9, 10

VCross variation

VCross-delta

140

mV

5, 9, 11

AC common mode

VSCK-cm-acp-p

225

mV

12

Rising and falling edge rates

ERRefclk-diff-Rise,

ERRefclk-diff-Fall

0.6

4.0

V/ns

6, 13

% Mismatch between rise and fall edge

rates

ERRefclk-Match

20

%

6, 14

Duty cycle of reference clock

TRefclk-Dutycycle

40

60

%

6

Ringback voltage threshold

VRB-diff

100

mV

6, 15

Allowed time before ringback

TStable

500

ps

6, 15

Clock leakage current

II_CK

10

A

16, 17

Clock input capacitance

CI_CK

0.5

2.0

pF

17

Clock input capacitance delta

CI_CK (

)

0.25

pF

Difference between

RefClk and RefClk#

input capacitance

Transport delay

TD

5

ns

18, 19

NSAMPLE

10

12

periods

20

Reference clock jitter (rms), filtered

TREF-JITTER-RMS

3.0

ps

21, 22

Reference clock jitter (peak-to-peak) due

to spectrum clocking effects

TREF-SSCp-p

30

ps

Reference clock jitter difference between

adjacent AMB

TREF-JITTER-

DELTA

0.75

ps

23

Notes: 1. For details, refer to the JEDEC specification “FB-DIMM High Speed Differential PTP Link at 1.5V”.

2. The nominal reference clock frequency is determined by the data frequency of the link divided by 2 times

the fixed PLL multiplication factor for the FB-DIMM channel (6:1). fdata = 2000MHz for a 4.0Gbps FB-

DIMM channel and so on.

3. Measured with SSC disabled. Enabling SSC will reduce the reference clock frequency.

4. Not all FB-DIMM agents will support all frequencies; compliance to the frequency specifications is only

required for those data rates that are supported by the device under test.

5. Measurement taken from single-ended waveform.

6. Measurement taken from differential waveform.

7. Defined as the maximum instantaneous voltage including overshoot.

8. Defined as the minimum instantaneous voltage including undershoot.

9. Measured at the crossing point where the instantaneous voltage value of the rising edge of REFCLK+

equals the falling edge of REFCLK-.

10. Refers to the total variation from the lowest crossing point to the highest, regardless of which edge is

crossing. Refers to all crossing points for this measurement.

11. Defined as the total variation of all crossing voltages of rising REFCLK+ and falling REFCLK-. This is the

maximum allowed variance in for any particular system.

12. The majority of the reference clock AC common mode occurs at high frequency (i.e., the reference clock

frequency).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EBR5334S | T-1 3/4 SINGLE COLOR LED, RED, 5 mm |

| EPY5334S | T-1 3/4 SINGLE COLOR LED, YELLOW GREEN, 5 mm |

| EC1448-D58U-00S | SINGLE PART CARD EDGE CONN |

| EC1SMG-20-24.576MTR | QUARTZ CRYSTAL RESONATOR, 24.576 MHz |

| EC2500SJT-FREQ3 | CRYSTAL OSCILLATOR, CLOCK, 53.125 MHz - 66.667 MHz, HCMOS/TTL OUTPUT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EBE41FE4ACWR | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:4GB Fully Buffered DIMM |

| EBE41FE4ACWR-6E-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:4GB Fully Buffered DIMM |

| EBE41FE4ACWT | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:4GB Fully Buffered DIMM |

| EBE41FE4ACWT-6E-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:4GB Fully Buffered DIMM |

| EBE41RE4AAHA | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:4GB Registered DDR2 SDRAM DIMM (512M words x 72 bits, 2 Ranks) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。