- 您現(xiàn)在的位置:買賣IC網 > PDF目錄384263 > CS61881 Octal E1 Analog Front EndLine Interface Units PDF資料下載

參數(shù)資料

| 型號: | CS61881 |

| 英文描述: | Octal E1 Analog Front EndLine Interface Units |

| 中文描述: | 八路素E1模擬前端底線接口單元 |

| 文件頁數(shù): | 13/28頁 |

| 文件大?。?/td> | 461K |

| 代理商: | CS61881 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

CS61881

DS451PP3

13

current instruction. The test data registers selected

by the current instruction retain their previous val-

ue.

2.7 JTAG Instruction Register (IR)

The 2-bit instruction register selects the test to be

performed and/or the data register to be accessed.

The valid instructions are shifted in LSB first and

are listed in Table 1.

2.7.1 EXTEST

The EXTEST instruction allows testing of off-chip

circuitry and board-level interconnect. EXTEST

connects the BSR to the TDI and TDO pins.

CS61881 inputs can be sampled by loading the

BSR with the Capture DR state. The sample values

can then be viewed by shifting the BSR register us-

ing the Shift-DR state. The device output pins can

be set by shifting a pattern into the boundary scan

register and then using the Update-DR state.

2.7.2 SAMPLE/PRELOAD

The SAMPLE/PRELOAD instruction samples all

device inputs and outputs. This instruction places

the BSR between the TDI and TDO pins. The BSR

is loaded with samples of the I/O pins by the Cap-

ture-DR state.

2.7.3 IDCODE

The IDCODE instruction connects the device iden-

tification register to the TDO pin. The device iden-

tification code can then be shifted out TDO using

the Shift-DR state

2.7.4 BYPASS

The BYPASS instruction connects a one TCK de-

lay register between TDI and TDO. The instruction

is used to bypass the device.

2.8 Boundary Scan Register (BSR)

The BSR is a shift register that provides access to

the digital I/O pins. The BSR is used to read and

write the device pins to verify interchip connectiv-

ity. Each pin has a corresponding scan cell in the

register. The pin to scan cell mapping is given in

the BSR description shown in Table 2.

Notes: 1)

Data is shifted LSB first into the BSR

register.

2) HIZ controls the RPOSx, RNEGx, and

RCLKx pins. When HIZ is High, the outputs

are enabled; when HIZ is Low, the outputs

are tri-stated.

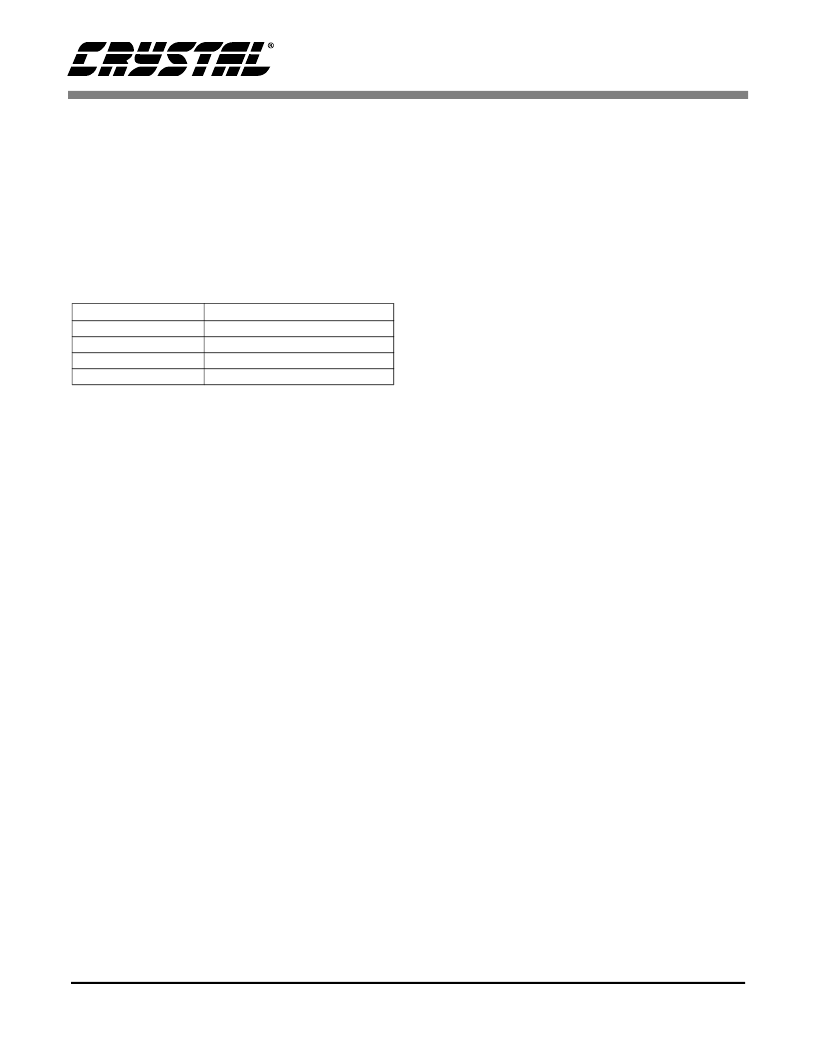

IR CODE

000

100

110

111

INSTRUCTION

EXTEST

SAMPLE/PRELOAD

IDCODE

BYPASS

Table 1. JTAG Instructions

相關PDF資料 |

PDF描述 |

|---|---|

| CS8130CS | Consumer IC |

| CS925 | |

| CSA562O | TRANSISTOR | BJT | PNP | 30V V(BR)CEO | 500MA I(C) | TO-92 |

| CSA562Y | TRANSISTOR | BJT | PNP | 30V V(BR)CEO | 500MA I(C) | TO-92 |

| CSA614O | TRANSISTOR | BJT | PNP | 55V V(BR)CEO | 3A I(C) | TO-220AB |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CS61881-IB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS61881-IQ | 制造商:Rochester Electronics LLC 功能描述:144TQFP - Bulk |

| CS61884 | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:Octal T1/E1/J1 Line Interface Unit |

| CS61884_05 | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:Octal T1/E1/J1 Line Interface Unit |

| CS61884-IB | 功能描述:網絡控制器與處理器 IC IC Octal T1/E1/J1 Line Interface Unit RoHS:否 制造商:Micrel 產品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。