- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374046 > ADV7175KS (ANALOG DEVICES INC) Integrated Digital CCIR-601 YCrCb to PAL/NTSC Video Encoder PDF資料下載

參數(shù)資料

| 型號(hào): | ADV7175KS |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 顏色信號(hào)轉(zhuǎn)換 |

| 英文描述: | Integrated Digital CCIR-601 YCrCb to PAL/NTSC Video Encoder |

| 中文描述: | COLOR SIGNAL ENCODER, PQFP44 |

| 封裝: | PLASTIC, QFP-44 |

| 文件頁數(shù): | 19/36頁 |

| 文件大?。?/td> | 447K |

| 代理商: | ADV7175KS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

ADV7175/ADV7176

REV. A

–19–

SUBCARRIE R FRE QUE NCY RE GIST E RS 3–0 (FSC3–FSC0)

(Address (SR4–SR0) = 05H–02H)

T hese 8-bit wide registers are used to set up the subcarrier fre-

quency. T he value of these registers are calculated by using the

following equation:

Subcarrier Frequency Register

=

2

32

±1

F

CLK

*

F

SCF

i.e.: NT SC Mode,

F

CLK

= 27 MHz, F

SCF

= 3.5796 MHz

S

ubcarrier Frequency Register

=

Subcarrier Frequency Register

= 21F07C16

HEX

Figure 33 shows how the frequency is set up by the 4 registers.

2

32

±1

27

×

10

6

*3.579545

×

10

6

SUBCARRIER

FREQUENCY

REG 0

SUBCARRIER

FREQUENCY

REG 1

SUBCARRIER

FREQUENCY

REG 2

SUBCARRIER

FREQUENCY

REG 3

FSC6

FSC5

FSC3

FSC1

FSC4

FSC2

FSC0

FSC7

FSC30 FSC29

FSC27

FSC25

FSC28

FSC26

FSC24

FSC31

FSC22 FSC21

FSC19

FSC17

FSC20

FSC18

FSC16

FSC23

FSC14 FSC13

FSC11

FSC9

FSC12

FSC10

FSC8

FSC15

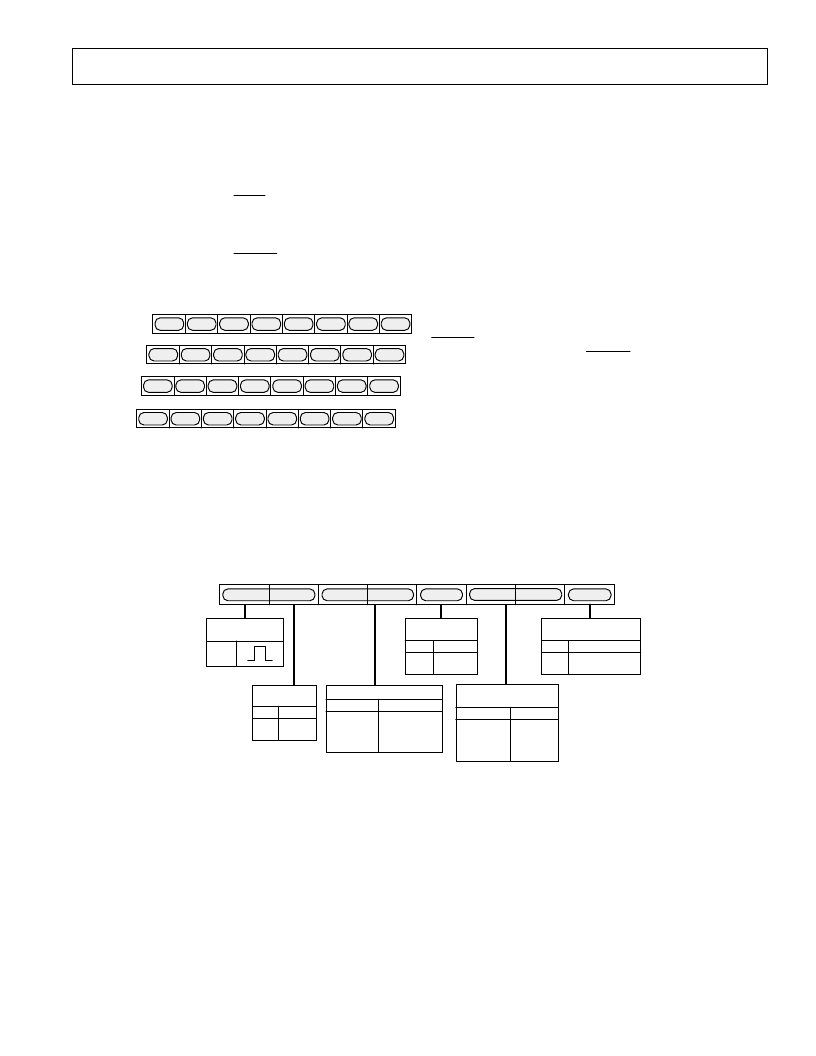

Figure 33. Subcarrier Frequency Register

SUBCARRIE R PHASE RE GIST E R (FP7–FP0):

(Address (SR4–SR0) = 06H)

T his 8-bit wide register is used to set up the subcarrier phase.

Each bit represents 1.41

°

.

T IMING RE GIST E R 0 (T R07–T R00)

(Address (SR4-SR0) = 07H)

T iming Register 0 is a 8-bit wide register.

Figure 34 shows the various operations under the control of

T iming Register 0. T his register can be read from as well

written to.

T IMING RE GIST E R 0 (T R07–T R00)

BIT DE SCRIPT ION

Master/Slave Control (T R00)

T his bit controls whether the ADV7175/ADV7176 is in master

or slave mode.

T iming Mode Control (T R02–T R01)

T hese bits control the timing mode of the ADV7175/ADV7176

T hese modes are described in the T iming and Control section

of the data sheet.

BLANK

Control (T R03)

T his bit controls whether the

BLANK

input is used when the

part is in slave mode.

Luma Delay Control (T R05–T R04)

T hese bits control the addition of a luminance delay. Each bit

represents a delay of 74 ns.

Pixel Port Select (T R06)

T his bit is used to set the pixel port to accept 8-bit or 16-bit

data. If an 8-bit input is selected the data will be set up on

Pins P7–P0.

T iming Register Reset (T R07)

T oggling T R07 from low to high and low again resets the inter-

nal timing counters. T his bit should be toggled after setting up a

new timing mode.

TR01

TR00

TR07

TR02

TR03

TR05

TR06

TR04

TIMING

REGISTER RESET

TR07

BLACK INPUT

CONTROL

TR03

0

1

ENABLE

DISABLE

PIXEL PORT

CONTROL

TR06

0

1

8-BIT

16-BIT

MASTER/SLAVE

CONTROL

TR00

0

1

SLAVE TIMING

MASTER TIMING

LUMA DELAY

0

0

1

1

0

1

0

1

0ns DELAY

74ns DELAY

148ns DELAY

222ns DELAY

TR05 TR04

TIMING MODE

SELECTION

0

0

1

1

0

1

0

1

MODE 0

MODE 1

MODE 2

MODE 3

TR02 TR01

Figure 34. Timing Register 0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7176 | Integrated Digital CCIR-601 YCrCb to PAL/NTSC Video Encoder |

| ADV7176KS | Integrated Digital CCIR-601 YCrCb to PAL/NTSC Video Encoder |

| ADV7177KS | Integrated Digital CCIR-601 to PAL/NTSC Video Encoder |

| ADV7177 | Integrated Digital CCIR-601 to PAL/NTSC Video Encoder |

| ADV7178 | Integrated Digital CCIR-601 to PAL/NTSC Video Encoder |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV7176 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Integrated Digital CCIR-601 YCrCb to PAL/NTSC Video Encoder |

| ADV7176A | 制造商:AD 制造商全稱:Analog Devices 功能描述:High Quality, 10-Bit, Digital CCIR-601 to PAL/NTSC Video Encoder |

| ADV7176AKS | 制造商:Analog Devices 功能描述:Video Encoder 4DAC 10-Bit 44-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:VIDEO ENCODER+TELETEXT(NTSC/PAL)I.C. - Bulk 制造商:Analog Devices 功能描述:IC VIDEO ENCODER |

| ADV7176AKSZ | 制造商:Analog Devices 功能描述:Video Encoder 4DAC 10-Bit 44-Pin MQFP 制造商:Analog Devices 功能描述:IC VIDEO ENCODER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。