- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374046 > ADV7162KS140 (ANALOG DEVICES INC) 96-Bit, 220 MHz True-Color Video RAM-DAC PDF資料下載

參數(shù)資料

| 型號: | ADV7162KS140 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 顯示控制器 |

| 英文描述: | 96-Bit, 220 MHz True-Color Video RAM-DAC |

| 中文描述: | 1600 X 1200 PIXELS PALETTE-DAC DSPL CTLR, PQFP160 |

| 封裝: | PLASTIC, QFP-160 |

| 文件頁數(shù): | 28/44頁 |

| 文件大?。?/td> | 668K |

| 代理商: | ADV7162KS140 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

REV. 0

–28–

ADV7160/ADV7162

COMMAND REGISTER 3 (CR3)

(Address Reg (A10–A0) = 007H)

This register contains a number of control bits as shown in the

diagram. CR3 is a 10-bit wide register. However for program-

ming purposes, it may be considered as an 8-bit wide register

(CR39 and CR38 are both reserved).

Figure 42 shows the various operations under the control of

CR3. This register can be read from as well written to. In write

mode zero should be written to CR35. In read mode, CR39 and

CR38 are returned as zeros.

COMMAND REGISTER 3 BIT DESCRIPTION

PRGCKOUT Frequency Control (CR31–CR30)

These bits specify the output frequency of the PRGCKOUT

output. PRGCKOUT is a divided down version of the pixel

CLOCK.

BLANK

Pipeline Delay Control (CR34–CR32)

These bits specify the additional pipeline delay that can be

added to the

BLANK

function, relative to the overall device

pipeline delay (t

PD

). As the

BLANK

control normally enters the

Video DAC from a shorter pipeline than the video pixel data,

this control is useful in de-skewing the pipeline differential.

Pixel Multiplex Control (CR37–CR36)

These bits specify the device’s multiplex mode. It therefore

also determines the frequency of the LOADOUT signal.

LOADOUT is a divided down version of the pixel CLOCK.

COMMAND REGISTER 2 (CR2)

(Address Reg (A10–A0) = 006H)

This register contains a number of control bits as shown in the

diagram. CR2 is a 10-bit wide register. However for program-

ming purposes, it may be considered as an 8-bit wide register

(CR29 and CR28 are both reserved).

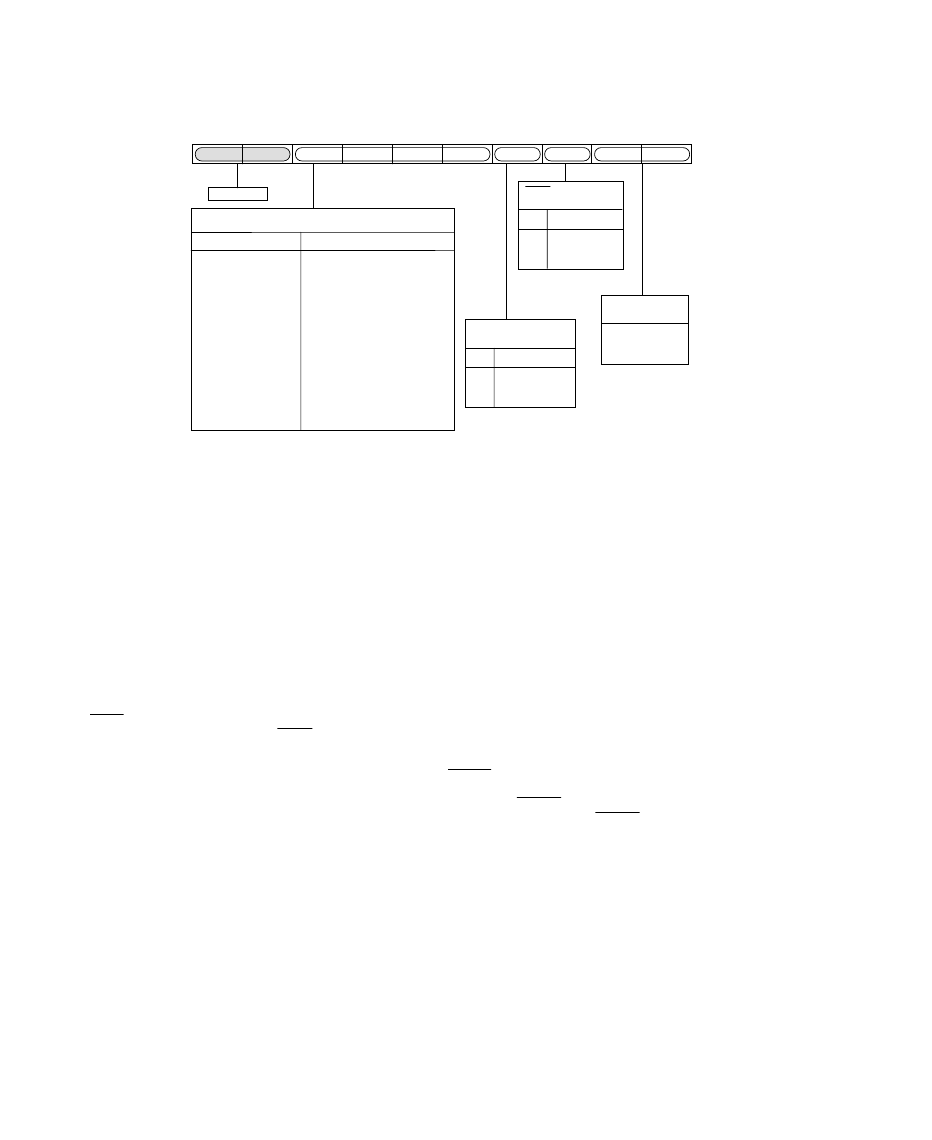

Figure 41 shows the various operations under the control of

CR2. This register can be read from as well written to. In write

mode zero should be written to CR21 and CR20. In read

mode, CR29 and CR28 are returned as zeros.

COMMAND REGISTER 2-BIT DESCRIPTION

SYNC

Recognition Control on Green (CR22)

This bit specifies whether the video

SYNC

Input is to be en-

coded onto the IOG analog output or ignored.

Pedestal Enable Control (CR23)

This bit specifies whether a 0 IRE or a 7.5 IRE blanking pedes-

tal is to be generated on the video outputs.

True-Color/Bypass/Pseudo-Color Mode Control (CR27–CR24)

These 4 bits specify the various color modes. These include a

24-bit true-color and bypass mode, one 16-bit true-color and

bypass mode, two 15-bit true-color modes, one 15-bit bypass

mode and three 8-bit pseudo color modes.

Figure 41. Command Register 2 (CR2) (CR29–CR20)

RESERVED*

CR29

CR28

CR27

CR26

CR20

CR25

CR24

CR21

*

THESE BITS ARE READ-ONLY RESERVED BITS.

A READ CYCLE WILL RETURN ZEROS "00."

CR21–CR20

(00)

ZERO SHOULD

BE WRITTEN TO

THESE BITS

SYNC

RECOGNITION

CONTROL (GREEN)

CR22

0 IGNORE

1 DECODE

PEDESTAL ENABLE

CONTROL

CR23

0 0 IRE

1 7.5 IRE

CR27 CR26 CR25 CR24

0 0 0 0 8-BIT PSEUDO COLOR ON R7–R0

0 1 0 0 8-BIT PSEUDO COLOR ON G7–G0

1 0 0 0 8-BIT PSEUDO COLOR ON B7–0

1 0 0 1 16-BIT BYPASS MODE USING

R7–R0, G7–G0

1 0 1 0 15-BIT BYPASS MODE USING

R6–R0, G7–G0

1 0 1 1 16-BIT TRUE COLOR ON R7–R0,

G7–G0

1 1 0 0 15-BIT TRUE COLOR ON R7–R3,

G7–G3, B7–B3

1 1 0 1 15-BIT TRUE COLOR ON R6–R0,

G7–G0

1 1 1 0 24-BIT TRUE COLOR

1 1 1 1 24-BIT BYPASS MODE

TRUE COLOR/PSEUDO COLOR MODE CONTROL

COLOR MODE

CR23

CR22

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7162KS170 | 96-Bit, 220 MHz True-Color Video RAM-DAC |

| ADV7162KS220 | 96-Bit, 220 MHz True-Color Video RAM-DAC |

| ADV7160KS140 | 96-Bit, 220 MHz True-Color Video RAM-DAC |

| ADV7160KS170 | 96-Bit, 220 MHz True-Color Video RAM-DAC |

| ADV7160KS220 | 96-Bit, 220 MHz True-Color Video RAM-DAC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV7162KS170 | 制造商:AD 制造商全稱:Analog Devices 功能描述:96-Bit, 220 MHz True-Color Video RAM-DAC |

| ADV7162KS220 | 制造商:Analog Devices 功能描述:DAC 3-CH Segment 10-bit 160-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:220 MHZ VIDEO RAM DAC I.C. - Bulk |

| ADV7162KSZ140 | 制造商:Analog Devices 功能描述:DAC 3-CH Segment 10-bit 160-Pin MQFP |

| ADV7162KSZ220 | 制造商:Analog Devices 功能描述:DAC 3-CH Segment 10-bit 160-Pin MQFP |

| ADV7170 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Digital PAL/NTSC Video Encoder with 10-Bit SSAF⑩ and Advanced Power Management |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。