- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄374037 > ADSP-BF532SBBC400 (ANALOG DEVICES INC) Blackfin Embedded Processor PDF資料下載

參數(shù)資料

| 型號(hào): | ADSP-BF532SBBC400 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類(lèi): | 數(shù)字信號(hào)處理 |

| 英文描述: | Blackfin Embedded Processor |

| 中文描述: | 16-BIT, 40 MHz, OTHER DSP, PBGA160 |

| 封裝: | MO-205AE, CSBGA-160 |

| 文件頁(yè)數(shù): | 22/56頁(yè) |

| 文件大小: | 671K |

| 代理商: | ADSP-BF532SBBC400 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)

Rev. 0

|

Page 22 of 56

|

March 2004

ADSP-BF531/ADSP-BF532/ADSP-BF533

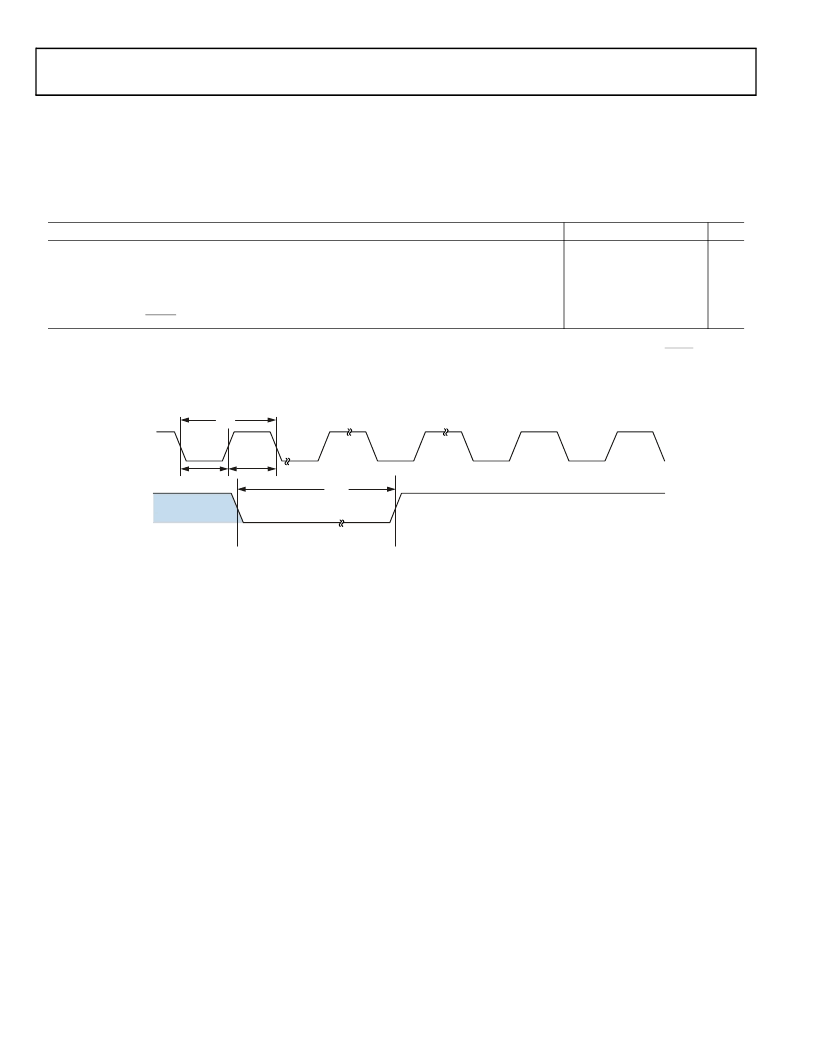

Clock and Reset Timing

Table 15

and

Figure 10

describe clock and reset operations. Per

Absolute Maximum Ratings on Page 20

, combinations of

CLKIN and clock multipliers must not select core/peripheral

clocks in excess of 600/133 MHz.

Table 15. Clock and Reset Timing

Parameter

Timing Requirements

t

CKIN

t

CKINL

t

CKINH

t

WRST

1

Applies to bypass mode and non-bypass mode.

2

Applies after power-up sequence is complete. At power-up, the processor’s internal phase-locked loop requires no more than 2000 CLKIN cycles, while RESET is asserted,

assuming stable power supplies and CLKIN (not including start-up time of external clock oscillator).

Min

Max

Unit

CLKIN Period

CLKIN Low Pulse

1

CLKIN High Pulse

1

RESET Asserted Pulse Width Low

2

25.0

10.0

10.0

11t

CKIN

100.0

ns

ns

ns

ns

Figure 10. Clock and Reset Timing

RESET

CLKIN

t

CKINH

t

CKINL

t

WRST

t

CKIN

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-BF532SBBZ400 | Blackfin Embedded Processor |

| ADSP-BF532SBST400 | 28-2 (14 Contacts) Pin Insert; For Use With:Amphenol MIL-C-5015 97 Series Circular Connectors; No. of Contacts:14; Gender:Male; Operating Voltage:1250V |

| ADSP-BF533 | Blackfin Embedded Processor |

| ADSP-BF533SBBC500 | Metal Connector Backshell |

| ADSP-BF533SBBZ500 | Blackfin Embedded Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-BF532SBBC400X | 制造商:Analog Devices 功能描述: |

| adsp-bf532sbb-c80 | 制造商:Analog Devices 功能描述: |

| adsp-bf532sbbc-c11 | 制造商:Analog Devices 功能描述: |

| adsp-bf532sbbc-dab | 制造商:Analog Devices 功能描述: |

| ADSPBF532SBBCENG | 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。