- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374037 > ADSP-2195MBST-140X (ANALOG DEVICES INC) DSP Microcomputer PDF資料下載

參數(shù)資料

| 型號: | ADSP-2195MBST-140X |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | DSP Microcomputer |

| 中文描述: | 16-BIT, 160 MHz, OTHER DSP, PQFP144 |

| 封裝: | METRIC, PLASTIC, LQFP-144 |

| 文件頁數(shù): | 36/68頁 |

| 文件大小: | 951K |

| 代理商: | ADSP-2195MBST-140X |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當(dāng)前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

For current information contact Analog Devices at 800/262-5643

ADSP-2195

September 2001

This information applies to a product under development. Its characteristics and specifications are subject to change with-

out notice. Analog Devices assumes no obligation regarding future manufacturing unless otherwise agreed to in writing.

36

REV. PrA

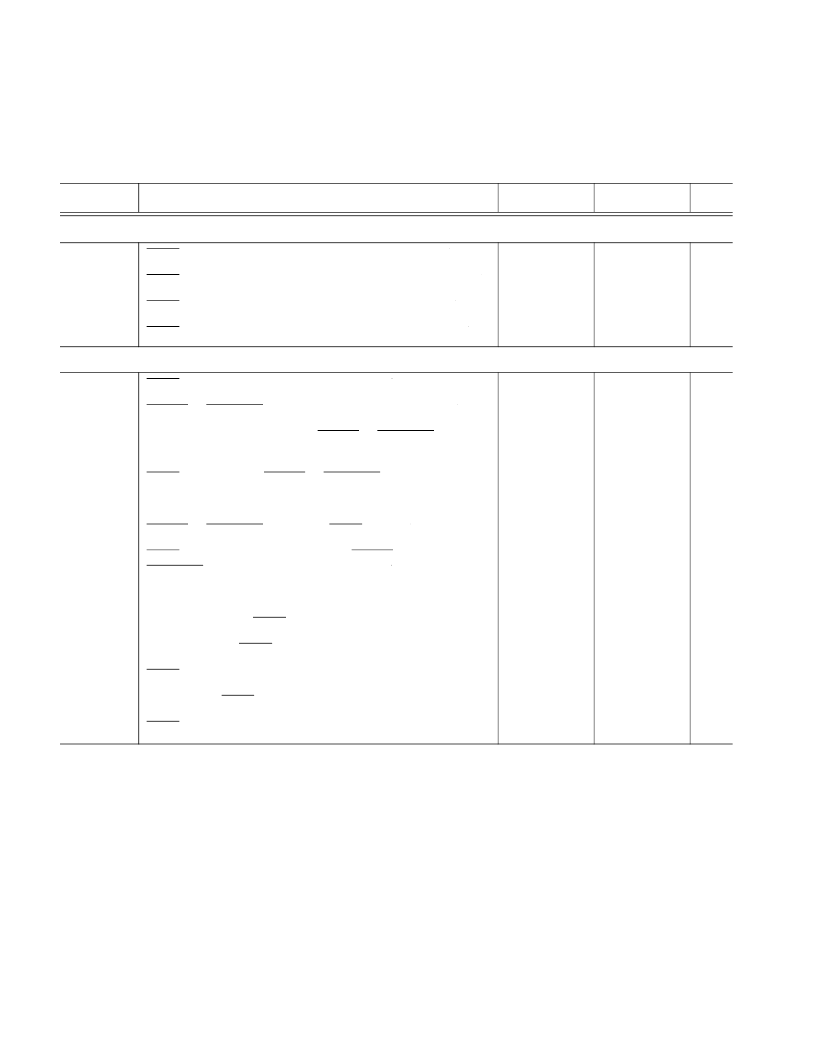

Host Port ACC Mode Write Cycle Timing

Table 15

and

Figure 18

describe host port write operations in Address Cycle Control (ACC) mode. For more information

on ACK, Ready, ALE, and ACC mode selection, see the Host port modes description

on page 10

.

Table 15. Host Port ACC Mode Write Cycle Timing

Parameter

Description

Min

Max

Unit

Switching Characteristics

t

WHKS

HWR asserted to HACK asserted (setup, ACK Mode)

0.6

0.6+t

NH

1

1

t

NH

are peripheral bus latencies (n

the same time.

t

HCLK

); these are internal DSP latencies related to the number of peripherals attempting to access DSP memory at

ns

t

WHKH

HWR de-asserted to HACK de-asserted (hold, ACK Mode)

2

ns

t

WHS

HWR asserted to HACK asserted (setup, Ready Mode)

0.6

ns

t

WHH

HWR asserted to HACK de-asserted (hold, Ready Mode)

2+t

NH

1

ns

Timing Requirements

t

WAL

HWR asserted to HALE de-asserted (delay)

1.5

ns

t

CSAL

HCMS or HCIOMS asserted to HALE asserted (delay)

0

ns

t

ALCS

HALE de-asserted to optional HCMS or HCIOMS

de-asserted

1

ns

t

WCSW

HWR de-asserted to HCMS or HCIOMS de-asserted

1

ns

t

ALW

HALE asserted to HWR asserted

0.5

ns

t

CSW

HCMS or HCIOMS asserted to HWR asserted

1

2

ns

t

WCS

HWR de-asserted (after last byte) to HCMS or

HCIOMS de-asserted (ready for next write)

1

ns

t

ALEW

HALE de-asserted to HWR asserted

1

ns

t

HKWD

HACK asserted to HWR de-asserted (hold, ACK Mode)

1.5

ns

t

ADW

Address valid to HWR asserted (setup)

4

ns

t

WAD

HWR de-asserted to address invalid (hold)

1

ns

t

DWS

Data valid to HWR de-asserted (setup)

4

ns

t

WDH

HWR de-asserted to data invalid (hold)

1

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-2195 | LM2991 Negative Low Dropout Adjustable Regulator; Package: CERDIP; No of Pins: 16; Qty per Container: 25; Container: Rail |

| ADSP-2195MBCA-140X | LM2991 Negative Low Dropout Adjustable Regulator; Package: CERDIP; No of Pins: 16; Container: Rail |

| ADSP-2195MKST-160X | LM2991 Negative Low Dropout Adjustable Regulator; Package: TO-263; No of Pins: 5; Qty per Container: 45; Container: Rail |

| ADSP-2196 | DSP Microcomputer |

| ADSP-2196MBCA-140X | DSP Microcomputer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-2195MKCA-160 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 24-Bit 160MHz 160MIPS 144-Pin CSP-BGA 制造商:Rochester Electronics LLC 功能描述:16-BIT,160 MIPS, 2.5V, 80KBYTES RAM - Bulk |

| ADSP-2195MKST-160 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 24-Bit 160MHz 160MIPS 144-Pin LQFP 制造商:Analog Devices 功能描述:IC MICROCOMPUTER 16-BIT |

| adsp-2196mbca-140 | 制造商:Analog Devices 功能描述: |

| adsp-2196mbst-140 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 140MHz 140MIPS 144-Pin LQFP 制造商:Rochester Electronics LLC 功能描述: |

| ADSP-2196MBST-140Z | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 140MHz 140MIPS 144-Pin LQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。