- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374035 > ADSP-2171KST-133 (ANALOG DEVICES INC) DSP Microcomputer PDF資料下載

參數(shù)資料

| 型號: | ADSP-2171KST-133 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | DSP Microcomputer |

| 中文描述: | 24-BIT, 16.67 MHz, OTHER DSP, PQFP128 |

| 封裝: | PLASTIC, TQFP-128 |

| 文件頁數(shù): | 19/52頁 |

| 文件大小: | 664K |

| 代理商: | ADSP-2171KST-133 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

ADSP-2171/ADSP-2172/ADSP-2173

REV. A

–19–

ADSP-2171/ADSP-2172

Parameter

Min

Max

Unit

Clock Signals

t

CK

is defined as 0.5 t

CK I.

T he ADSP-2171/ADSP-2172 uses an

input clock with a frequency equal to half the instruction rate; a

clock (which is equivalent to 60 ns) yields a 30 ns processor cycle

16.67 MHz input (equivalent to 33 MHz). t

CK

values within the

range of 0.5 t

CK I

period should be substituted for all relevant

timing parameters to obtain specification value.

Example: t

CK H

= 0.5t

CK

– 7 ns = 0.5 (30 ns) – 7 ns = 8 ns.

T iming Requirement:

t

CK I

t

CK IL

t

CK IH

CLK IN Period

CLK IN Width Low

CLK IN Width High

60

20

20

150

ns

ns

ns

Switching Characteristic:

t

CK L

t

CK H

t

CK OH

CLK OUT Width Low

CLK OUT Width High

CLK IN High to CLK OUT High

0.5t

CK

– 7

0.5t

CK

– 7

0

ns

ns

ns

20

Control Signals

T iming Requirement:

t

RSP

RESET Width Low

5t

CK1

ns

NOT E

1

Applies after power-up sequence is complete. Internal phase lock loop requires no more than 2000 CLK IN cycles assuming stable CLK IN (not including crystal

oscillator start-up time).

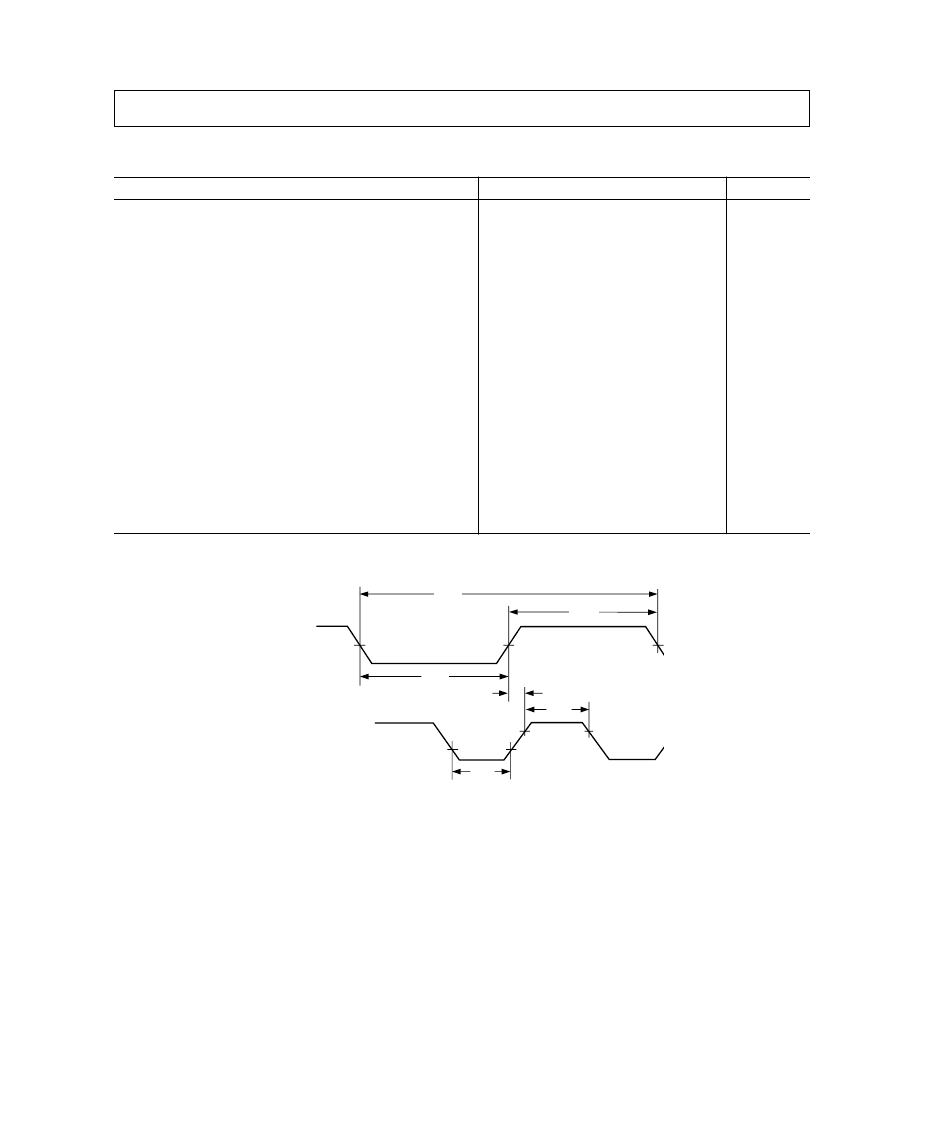

CLKIN

CLKOUT

t

CKIL

t

CKOH

t

CKH

t

CKL

t

CKI

t

CKIH

Figure 8. Clock Signals

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADSP-2171BST-104 | DSP Microcomputer |

| ADSP-2171BST-133 | DSP Microcomputer |

| ADSP-2173BS-80 | DSP Microcomputer |

| ADSP-2171 | DSP Microcomputer(DSP 微計(jì)算機(jī)) |

| ADSP-2172 | DSP Microcomputer(DSP 微計(jì)算機(jī)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-2172 | 制造商:AD 制造商全稱:Analog Devices 功能描述:DSP Microcomputer |

| ADSP-2173 | 制造商:AD 制造商全稱:Analog Devices 功能描述:DSP Microcomputer |

| ADSP-2173BS-80 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| ADSP-2173BST-80 | 制造商:Analog Devices 功能描述:DSP Fixed-Point 16-Bit 20MHz 20MIPS 128-Pin TQFP 制造商:Rochester Electronics LLC 功能描述:16BIT FXD PT PROC 3.3V - Bulk |

| ADSP-2176-760040 | 制造商:Analog Devices 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。