- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375252 > ADAU1701 (Analog Devices, Inc.) SigmaDSP 28/56-Bit Audio Processor with 2ADC/4DAC PDF資料下載

參數(shù)資料

| 型號: | ADAU1701 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | SigmaDSP 28/56-Bit Audio Processor with 2ADC/4DAC |

| 中文描述: | SigmaDSP的28/56-Bit音頻處理器2ADC/4DAC |

| 文件頁數(shù): | 19/43頁 |

| 文件大小: | 625K |

| 代理商: | ADAU1701 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

Preliminary Technical Data

ADAU1701

CONTROL PORT

OVERVIEW

The ADAU1701 can operate in one of three control modes:

Rev. PrF | Page 19 of 43

I

2

C Control

SPI Control

Selfboot (no external controller)

The ADAU1701 has both a 4-wire SPI control port, and a 2-

wire I

2

C bus control port that can each be used to set the part’s

RAMs and registers. When selfboot mode is not selected at

power-up, the part defaults to I

2

C mode, but can be put into SPI

control mode by pulling pin CLATCH/WP low three times.

When the SELFBOOT pin is set high, the ADAU1701 will load

its program, parameters, and registers settings from an external

EEPROM on start-up.

The control port is capable of full read/write operation for all of

the memories and registers. Most signal processing parameters

are controlled by writing new values to the parameter RAM

using the control port. Other functions, such as mute and

input/output mode control, are programmed by writing to the

control registers.

All addresses may be accessed in both a single-address mode or

a burst mode. A control word consists of the chip address, the

register/RAM subaddress, and the data to be written. The

number of bytes per word depends on the type of data that is

written.

The first byte of a control word (Byte 0) contains the 7-bit chip

address plus the R/W bit. The next two bytes (Bytes 1 and 2)

together form the subaddress of the memory or register

location within the ADAU1701. This subaddress needs to be

two bytes because the memories within the ADAU1701 are

directly addressable, and their sizes exceed the range of single-

byte addressing. All subsequent bytes (Bytes 3, 4, etc.) contain

the data, such as control port data or program or parameter

data. The exact formats for specific types of writes are shown in

Table 27 to Table 35.

The ADAU1701 has several mechanisms for updating signal

processing parameters in real time without causing pops or

clicks. In cases where large blocks of data need to be down-

loaded, the output of the DSP core can be halted (using Bit x of

the core control register), new data loaded, and then restarted.

This is typically done during the booting sequence at start-up or

when loading a new program into RAM. In cases where only a

few parameters need to be changed, they can be loaded without

halting the program. To avoid unwanted side effects while

loading parameters on the fly, the SigmaDSP provides the

safeload registers. The safeload registers can be used to buffer a

full set of parameters (e.g. the five coefficients of a biquad) and

then transfer these parameters into the active program within

one audio frame. The safeload mode uses internal logic to

prevent contention between the DSP core and the control port.

The control port pins are multi-functional according to which

mode in which the part is operating. details these different

functions.

I

2

C PORT

The ADAU1701 supports a 2-wire serial (I

2

C compatible)

microprocessor bus driving multiple peripherals. Two pins,

serial data (SDA) and serial clock (SCL), carry information

between the ADAU1701 and the system I

2

C master controller.

In I

2

C mode the ADAU1701 is always a slave on the bus, which

means that it will never initiate a data transfer. Each slave device

is recognized by a unique address. The address byte format is

shown in Table 15. The ADAU1701 has four possible slave

addresses: two for writing operations and two for reading.

These are unique addresses for the device and are illustrated in

Table 16. The LSB of the byte sets either a read or write

operation; Logic Level 1 corresponds to a read operation, and

Logic Level 0 corresponds to a write operation. The sixth and

seventh bits of the address are set by tying the ADDRx pins of

the ADAU1701 to logic level 0 or logic level 1. Both SDA and

SCL should have 2.2 kΩ pull-up resistors on the lines connected

to them. The voltage on these signal lines should not be above

IOVDD (3.3 V).

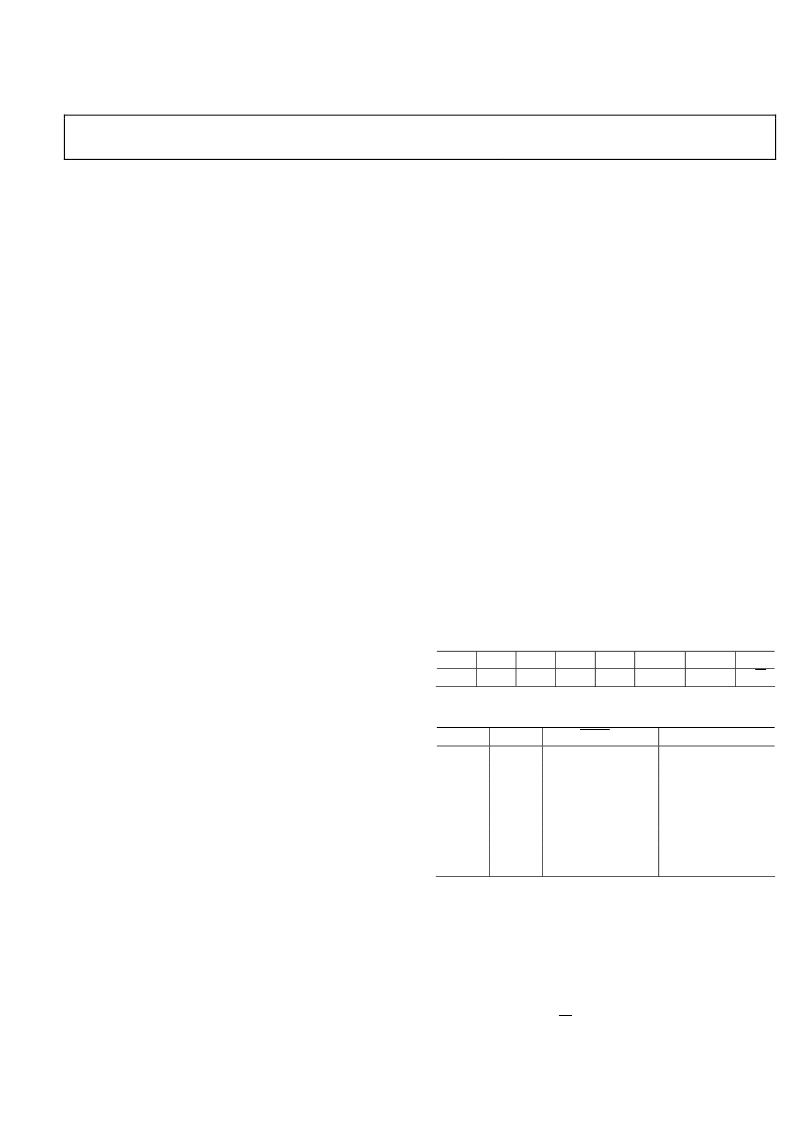

Table 15. ADAU1701 Address Byte Format

Bit 0

Bit 1

Bit 2

Bit 3

Bit 4

0

1

1

0

Bit 5

ADDR1

Bit 6

ADDR0

Bit 7

R/W

1

Table 16. ADAU1701 I

2

C Addresses

ADDR1

ADDR0

0

0

0

0

0

1

0

1

1

0

1

0

1

1

1

1

Addressing

Initially, all devices on the I

2

C bus are in an idle state, which is

where the devices monitor the SDA and SCL lines for a start

condition and the proper address. The I

2

C master initiates a

data transfer by establishing a Start condition, defined by a

high-to-low transition on SDA while SCL remains high. This

indicates that an address/data stream will follow. All devices on

the bus respond to the start condition and shift the next eight

bits (7-bit address + R/W bit) MSB first. The device that

recognizes the transmitted address responds by pulling the data

Read/Write

0

1

0

1

0

1

0

1

Slave Address

0x68

0x69

0x6A

0x6B

0x6C

0x6D

0x6E

0x6F

相關PDF資料 |

PDF描述 |

|---|---|

| ADAU1701JSTZ | SigmaDSP 28/56-Bit Audio Processor with 2ADC/4DAC |

| ADAU1701JSTZ-RL | SigmaDSP 28/56-Bit Audio Processor with 2ADC/4DAC |

| ADAV400 | Audio Codec with Embedded SigmaDSP Processor |

| ADAV400KSTZ | Audio Codec with Embedded SigmaDSP Processor |

| ADAV400KSTZ-REEL | Audio Codec with Embedded SigmaDSP Processor |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ADAU1701JSTZ | 功能描述:IC AUDIO PROC 2ADC/4DAC 48-LQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 音頻處理 系列:SigmaDSP® 其它有關文件:STA321 View All Specifications 標準包裝:1 系列:Sound Terminal™ 類型:音頻處理器 應用:數(shù)字音頻 安裝類型:表面貼裝 封裝/外殼:64-LQFP 裸露焊盤 供應商設備封裝:64-LQFP EP(10x10) 包裝:Digi-Reel® 其它名稱:497-11050-6 |

| ADAU1701JSTZ-RL | 功能描述:IC AUDIO PROC 2ADC/4DAC 48-LQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 音頻處理 系列:SigmaDSP® 其它有關文件:STA321 View All Specifications 標準包裝:1 系列:Sound Terminal™ 類型:音頻處理器 應用:數(shù)字音頻 安裝類型:表面貼裝 封裝/外殼:64-LQFP 裸露焊盤 供應商設備封裝:64-LQFP EP(10x10) 包裝:Digi-Reel® 其它名稱:497-11050-6 |

| ADAU1701MINIBZ | 制造商:Analog Devices 功能描述:EVAL BD SIGMADSPMULTICHANAUDIO PROCESSOR - Bulk |

| ADAU1702 | 制造商:AD 制造商全稱:Analog Devices 功能描述:SigmaDSP 28-56-Bit Audio Processor with Two ADCs and Four DACs |

| ADAU1702JSTZ | 功能描述:IC AUDIO PROC 2ADC/4DAC 48-LQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 音頻處理 系列:SigmaDSP® 其它有關文件:STA321 View All Specifications 標準包裝:1 系列:Sound Terminal™ 類型:音頻處理器 應用:數(shù)字音頻 安裝類型:表面貼裝 封裝/外殼:64-LQFP 裸露焊盤 供應商設備封裝:64-LQFP EP(10x10) 包裝:Digi-Reel® 其它名稱:497-11050-6 |

發(fā)布緊急采購,3分鐘左右您將得到回復。