- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375238 > AD7715 (Analog Devices, Inc.) 3 V/5 V, 450 mA 16-Bit, Sigma-Delta ADC(16位∑△A/D轉(zhuǎn)換器) PDF資料下載

參數(shù)資料

| 型號(hào): | AD7715 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 3 V/5 V, 450 mA 16-Bit, Sigma-Delta ADC(16位∑△A/D轉(zhuǎn)換器) |

| 中文描述: | 3伏/ 5伏,450毫安16位Σ-Δ模數(shù)轉(zhuǎn)換器(16位Σ△的A / D轉(zhuǎn)換器) |

| 文件頁(yè)數(shù): | 2/31頁(yè) |

| 文件大小: | 254K |

| 代理商: | AD7715 |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)

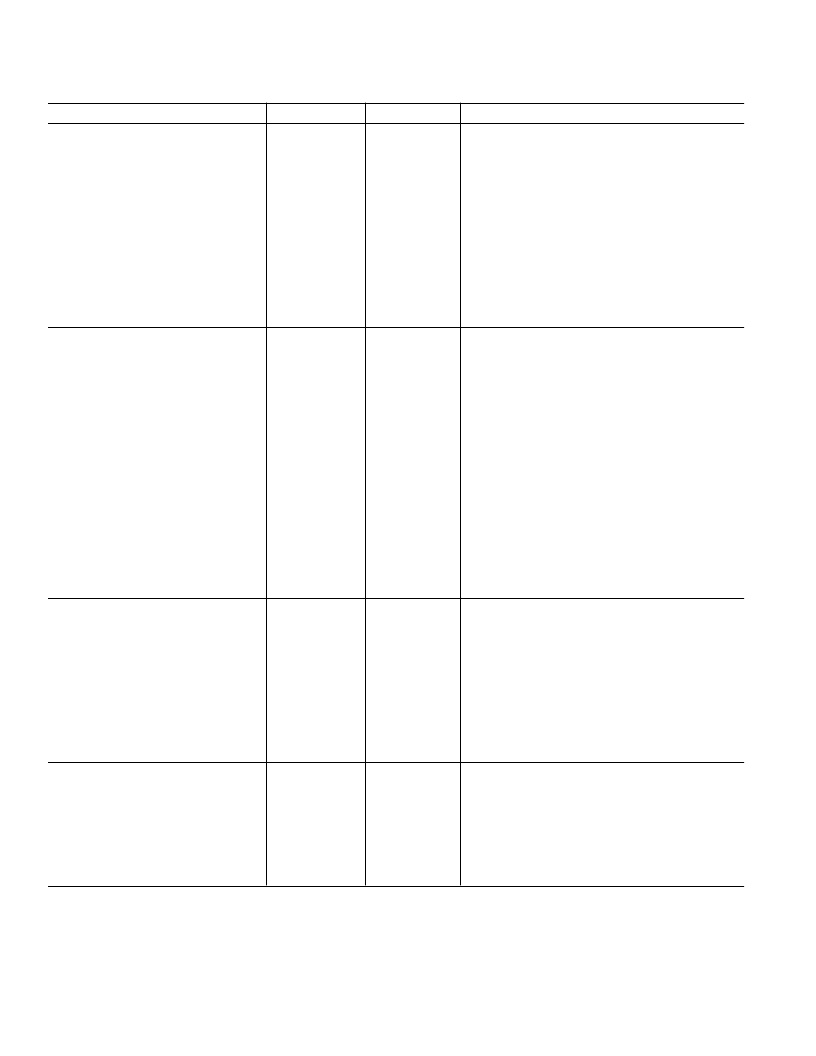

Parameter

A Version

1

Units

Conditions/Comments

STATIC PERFORMANCE

No Missing Codes

Output Noise

Integral Nonlinearity

Unipolar Offset Error

Unipolar Offset Drift

3

Bipolar Zero Error

Bipolar Zero Drift

3

Positive Full-Scale Error

4

Full-Scale Drift

3, 5

Gain Error

6

Gain Drift

3, 7

Bipolar Negative Full-Scale Error

2

Bipolar Negative Full-Scale Drift

3

16

See Tables V to VIII

±

0.0015

See Note 2

0.5

See Note 2

0.5

See Note 2

0.5

See Note 2

0.5

±

0.0015

1

0.6

Bits min

Guaranteed by Design. Filter Notch

≤

60Hz

Depends on Filter Cutoffs and Selected Gain

Filter Notch

≤

60Hz

% of FSR max

μ

V/

°

C typ

μ

V/

°

C typ

μ

V/

°

C typ

ppm of FSR/

°

C typ

% of FSR max

μ

V/

°

C typ

μ

V/

°

C typ

Typically

±

0.0004%

For Gains of 1 and 2

For Gains of 32 and 128

Specifications for AIN and REF IN Unless Noted

at DC. Typically 102 dB

For Filter Notches of 25 Hz, 50 Hz,

±

0.02

×

f

NOTCH

For Filter Notches of 20 Hz, 60 Hz,

±

0.02

×

f

NOTCH

For Filter Notches of 25 Hz, 50 Hz,

±

0.02

×

f

NOTCH

For Filter Notches of 20 Hz, 60 Hz,

±

0.02

×

f

NOTCH

AIN for BUF Bit of Setup Register = 0 and REF IN

AIN for BUF Bit of Setup Register = 0 and REF IN

ANALOG INPUTS/REFERENCE INPUTS

Input Common-Mode Rejection (CMR)

Normal-Mode 50 Hz Rejection

8

Normal-Mode 60 Hz Rejection

8

Common-Mode 50 Hz Rejection

8

Common-Mode 60 Hz Rejection

8

Common-Mode Voltage Range

9

Absolute AIN/REF IN Voltage

8

90

98

98

150

150

AGND to AV

DD

AGND – 30 mV

AV

DD

+ 30mV

AGND + 50mV

AV

DD

– 1.5V

1

10

0 to +V

REF

/GAIN

11

±

V

REF

/GAIN

GAIN

×

f

CLKIN

/64

f

CLKIN

/8

+2.5

dB min

dB min

dB min

dB min

dB min

V min to V max

V min

V max

V min

V max

nA max

pF max

nom

nom

Absolute/Common-Mode AIN Voltage

9

BUF Bit of Setup Register = 1

AIN DC Input Current

8

AIN Sampling Capacitance

8

AIN Differential Voltage Range

10

Unipolar Input Range (B/U Bit of Setup Register = 1)

Bipolar Input Range (B/U Bit of Setup Register = 0)

For Gains of 1 and 2

For Gains of 32 and 128

±

1% for Specified Performance. Functional with

Lower V

REF

AIN Input Sampling Rate, f

S

REF IN(+) – REF IN(–) Voltage

V nom

REF IN Input Sampling Rate, f

S

LOGIC INPUTS

Input Current

All Inputs Except MCLK IN

V

INL

, Input Low Voltage

V

INL

, Input Low Voltage

V

INH

, Input High Voltage

V

INH

, Input High Voltage

MCLK IN Only

V

INL

, Input Low Voltage

V

INL

, Input Low Voltage

V

INH

, Input High Voltage

V

INH

, Input High Voltage

LOGIC OUTPUTS (Including MCLK OUT)

V

OL

, Output Low Voltage

V

OL

, Output Low Voltage

V

OH

, Output High Voltage

V

OH

, Output High Voltage

Floating State Leakage Current

Floating State Output Capacitance

13

Data Output Coding

f

CLK IN

/64

±

10

μ

A max

0.8

0.4

2.4

2.0

V max

V max

V min

V min

DV

DD

= +5V

DV

DD

= +3.3V

DV

DD

= +5 V

0.8

0.4

3.5

2.5

V max

V max

V min

V min

DV

DD

= +5V

DV

DD

= +3.3V

DV

DD

= +5V

DV

DD

= +3.3V

0.4

0.4

4.0

DV

DD

– 0.6 V

±

10

9

Binary

Offset Binary

V max

V max

V min

V min

μ

A max

pF typ

I

SINK

= 800

μ

A Except for MCLK OUT

12

. DV

DD

= +5V

I

SINK

= 100

μ

A Except for MCLK OUT

12

. DV

DD

= +3.3V

I

SOURCE

= 200

μ

A Except for MCLK OUT

12

. DV

DD

= +5V

I

SOURCE

= 100

μ

A Except for MCLK OUT

12

. DV

DD

= +3.3V

Unipolar Mode

Bipolar Mode

AD7715-5–SPECIFICATIONS

(AV

DD

= +5V, DV

DD

= +3V or +5V, REF IN(+) = +2.5V; REFIN(–) = AGND;

f

CLK IN

= 2.4576MHz unless otherwise noted. All specifications T

MIN

to T

MAX

unless otherwise noted.)

REV. B

–2–

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7716BP | LC2MOS 22-Bit Data Acquisition System |

| AD7716BS | LC2MOS 22-Bit Data Acquisition System |

| AD7716 | 22-Bit Data Acquisition System(LC2MOS 22位數(shù)據(jù)采集系統(tǒng)) |

| AD7734 | 4-Channel, +-10 V Input Range, High Throughput, 24-Bit sigma ∆ ADC |

| AD7734BRU | 4-Channel, +-10 V Input Range, High Throughput, 24-Bit sigma ∆ ADC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7715_10 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, 450 ??A 16-Bit, Sigma-Delta ADC |

| AD7715-5EB | 制造商:Analog Devices 功能描述: |

| AD7715ACHIPS-3 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, 450 uA 16-Bit, Sigma-Delta ADC |

| AD7715ACHIPS-5 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, 450 uA 16-Bit, Sigma-Delta ADC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。