- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382789 > μPD784046(A) (NEC Corp.) 16 Bit Single Chip Microcontrollers(16 位單片微控制器) PDF資料下載

參數(shù)資料

| 型號: | μPD784046(A) |

| 廠商: | NEC Corp. |

| 英文描述: | 16 Bit Single Chip Microcontrollers(16 位單片微控制器) |

| 中文描述: | 16位單片機微控制器(16位單片微控制器) |

| 文件頁數(shù): | 66/90頁 |

| 文件大小: | 613K |

| 代理商: | ΜPD784046(A) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁當(dāng)前第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁

μ

PD784044(A), 784046(A)

66

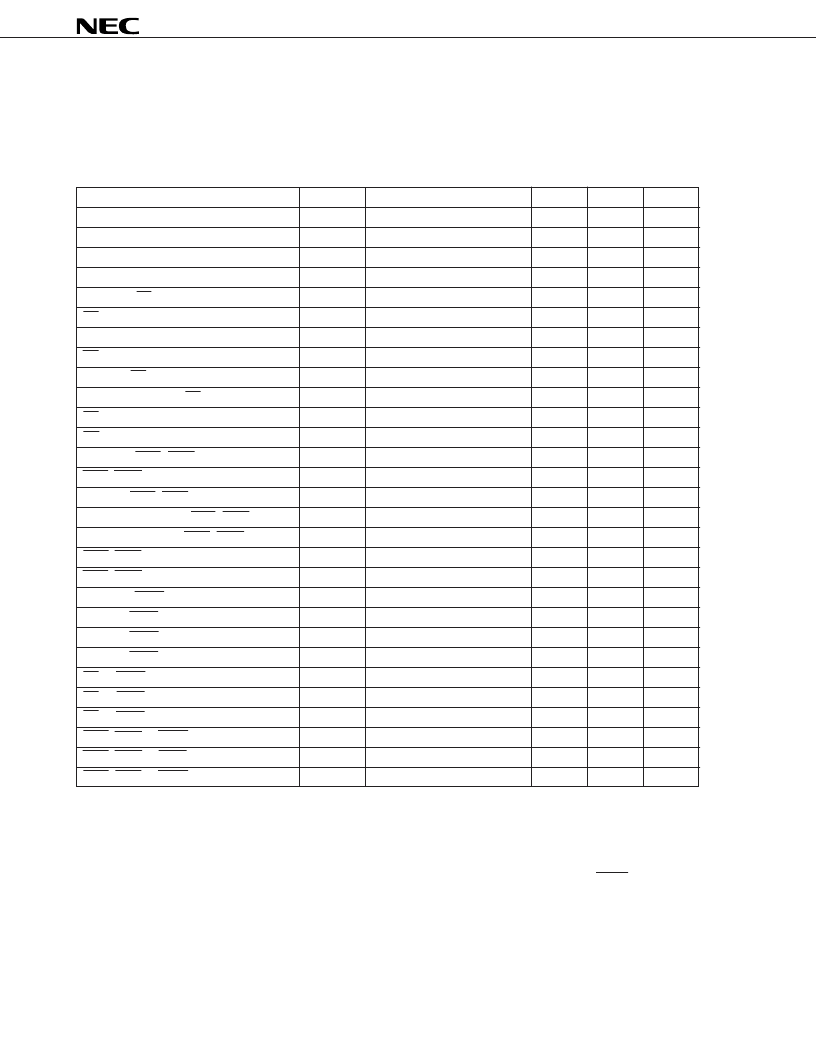

(2) Electrical specifications of

μ

PD784044(A1), 784046(A1) (4/6)

AC Characteristics (T

A

= –40 to +110 C, V

DD

= 4.5 to 5.5 V, V

SS

= 0 V)

Read/write operation

Parameter

Symbol

Expression

MIN.

MAX.

Unit

System clock cycle time

t

CYK

100

250

ns

Address setup time (vs. ASTB

↓

)

t

SAST

(0.5 + a) T – 20

30

ns

Address hold time (vs. ASTB

↓

)

t

HSTA

0.5T – 20

30

ns

ASTB high-level width

t

WSTH

(0.5 + a) T – 17

33

ns

Address

→

RD

↓

delay time

t

DAR

(1 + a) T – 15

85

ns

RD

↓→

address float time

t

FRA

0

ns

Address

→

data input time

t

DAID

(2.5 + a + n) T – 56

194

ns

RD

↓→

data input time

t

DRID

(1.5 + n) T – 53

97

ns

ASTB

↓→

RD

↓

delay time

t

DSTR

0.5T – 16

34

ns

Data hold time (vs. RD

↑

)

t

HRID

0

ns

RD

↑→

address active time

t

DRA

0.5T – 14

36

ns

RD low-level width

t

WRL

(1.5 + n) T – 30

120

ns

Address

→

LWR, HWR

↓

delay time

t

DAW

(1 + a) T – 15

85

ns

LWR, HWR

↓→

data output time

t

DWOD

15

ns

ASTB

↓→

LWR, HWR

↓

delay time

t

DSTW

0.5T – 16

34

ns

Data setup time (vs. LWR, HWR

↑

)

t

SODW

(1.5 + n) T – 25

125

ns

Data hold time (vs. LWR, HWR

↑

)

t

HWOD

0.5T – 14

36

ns

LWR, HWR

↑→

ASTB

↑

delay time

t

DWST

1.5T – 15

135

ns

LWR, HWR low-level width

t

WWL

(1.5 + n) T – 36

114

ns

Address

→

WAIT

↓

input time

t

DAWT

(2 + a) T – 50

150

ns

ASTB

↓→

WAIT

↓

input time

t

DSTWT

1.5T – 40

110

ns

ASTB

↓→

WAIT hold time

t

HSTWT

(1.5 + n) T + 5

155

ns

ASTB

↓→

WAIT

↑

delay time

t

DSTWTH

(1.5 + n) T – 40

210

Note

ns

RD

↓→

WAIT

↓

input time

t

DRWT

T – 40

60

ns

RD

↓→

WAIT hold time

t

HRWT

(1 + n) T + 5

105

ns

RD

↓→

WAIT

↑

delay time

t

DRWTH

(1 + n) T – 40

160

Note

ns

LWR, HWR

↓→

WAIT

↓

input time

t

DWWT

T – 40

60

ns

LWR, HWR

↓→

WAIT hold time

t

HWWT

(1 + n) T + 5

105

ns

LWR, HWR

↓→

WAIT

↑

delay time

t

DWWTH

(1 + n) T – 40

160

Note

ns

Note

Specification when an external wait is inserted

Remarks 1.

T = t

CYK

= 1/f

CLK

(f

CLK

is internal system clock frequency)

2.

a = 1 when an address wait is inserted, otherwise, 0.

3.

n indicates the number of the wait cycles by specifying the external wait pins (WAIT) or program-

mable wait control registers 1, 2 (PWC1, PWC2). (n

≥

0. n

≥

1 for t

DSTWTH

, t

DRWTH

, t

DWWTH

).

4.

Calculate values in the expression column with the system clock cycle time to be used because

these values depend on the system clock cycle time (t

CYK

= T). The values in the above expression

column are calculated based on T = 100 ns.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| μPD784046 | 16 Bit Single Chip Microcontrollers(16位單片微控制器) |

| μPD784044 | 16 Bit Single Chip Microcontrollers(16位單片微控制器) |

| μPD784054 | 16 Bit Single Chip Microcontrollers(16位單片微控制器) |

| μPD789011 | 8 Bit Single Chip Microcontrollers(8位單片微控制器) |

| μPD789012 | 8 Bit Single Chip Microcontrollers(8位單片微控制器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PD784054GCA2 | 制造商:NEC 制造商全稱:NEC 功能描述:16-BIT SINGLE-CHIP MICROCONTROLLER |

| PD784976A | 制造商:NEC 制造商全稱:NEC 功能描述:16-Bit Single-Chip Microcontroller |

| PD7869 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Optoelectronic |

| PD78F0134 | 制造商:NEC 制造商全稱:NEC 功能描述:8-Bit Single-Chip Microcontrollers |

| PD78F0134(A) | 制造商:NEC 制造商全稱:NEC 功能描述:8-Bit Single-Chip Microcontrollers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。