- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄2019 > XRT71D04IV (Exar Corporation)IC JITTER ATTENUATOR 4CH 80TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XRT71D04IV |

| 廠商: | Exar Corporation |

| 文件頁(yè)數(shù): | 17/22頁(yè) |

| 文件大小: | 0K |

| 描述: | IC JITTER ATTENUATOR 4CH 80TQFP |

| 標(biāo)準(zhǔn)包裝: | 94 |

| 類(lèi)型: | * |

| PLL: | 是 |

| 輸入: | 時(shí)鐘 |

| 輸出: | 時(shí)鐘 |

| 電路數(shù): | 1 |

| 比率 - 輸入:輸出: | 4:3 |

| 差分 - 輸入:輸出: | 無(wú)/無(wú) |

| 頻率 - 最大: | 44.736MHz |

| 除法器/乘法器: | 無(wú)/無(wú) |

| 電源電壓: | 3.135 V ~ 5.25 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 80-LQFP |

| 供應(yīng)商設(shè)備封裝: | 80-TQFP(14x14) |

| 包裝: | 托盤(pán) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)

XRT71D04

á

4 CHANNEL E3/DS3/STS-1 JITTER ATTENUATOR, STS-1 TO DS3 DESYNCHRONIZER

REV. 1.1.1

3

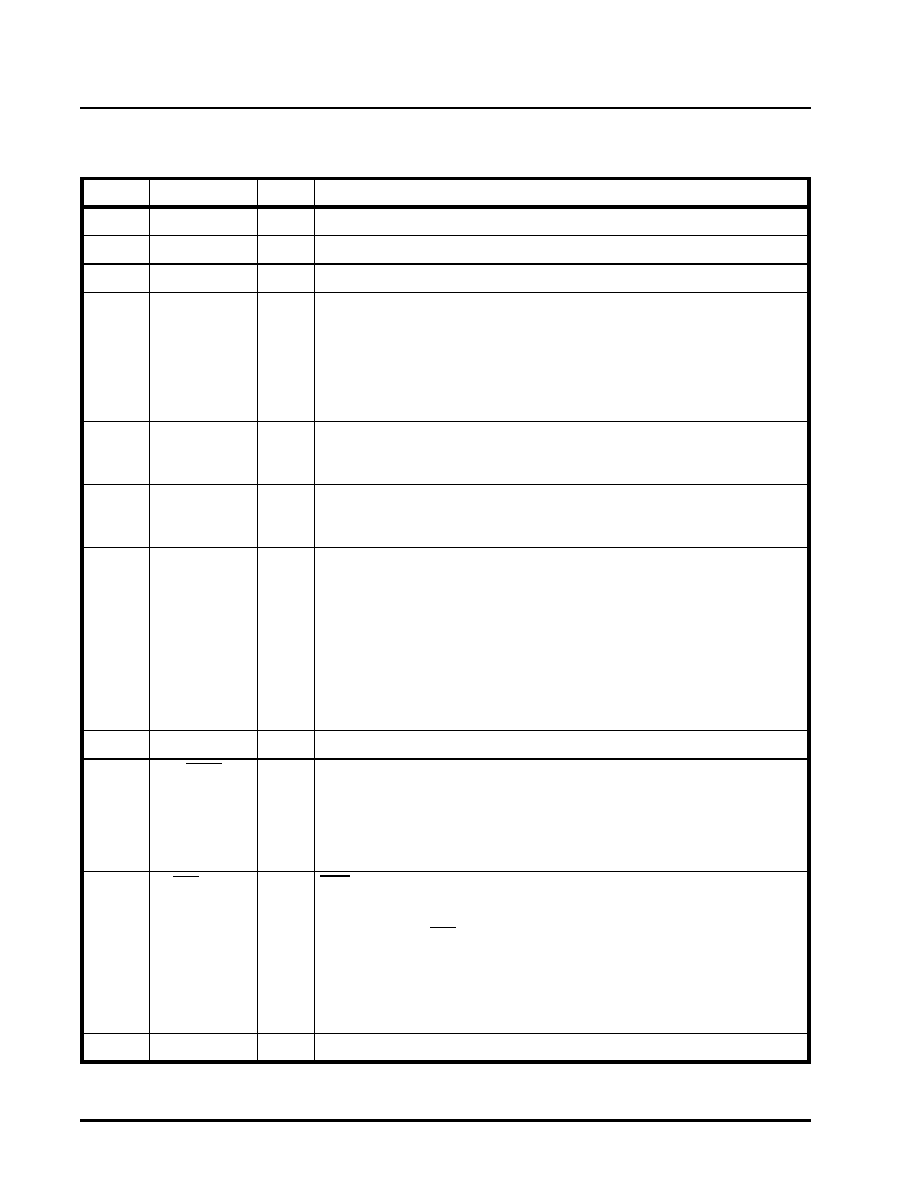

PIN DESCRIPTIONS

PIN DESCRIPTION

PIN #NAME

TYPE

DESCRIPTION

1

AVDD

****

Analog Power Supply = 5V±5% or 3.3V±5%

2

NC

No Connection

3

GND

****

Digital Ground

4

RRCLK_0

O

Received Recovered Output (De-jittered) Clock - channel 0:

Output is the de-jittered or smoothed clock if the jitter attenuator is enabled. The

de-jittered data, RRPOS/RRNEG are clocked to this signal.

If RRCLKES is “l(fā)ow”, RRPOS/RRNEG will be updated at the falling edge of

RRCLK.

If RRCLKES is “high”, RRPOS/RRNEG will be updated at the rising edge of

RRCLK.

5

RRPOS_0

O

Received Recovered Positive Data (De-Jittered) Output - channel 0:

De-jittered positive data output. Updated on the rising or falling edge of RRCLK,

depending upon the state of the RRCLKES input pin (or bit-field setting).

6

RRNEG_0

O

Received Recovered Negative Data (De-Jittered) Output - channel 0:

De-jittered negative data output. Updated on the rising or falling edge of RRCLK,

depending upon the state of the RRCLKES input pin (or bit-field setting).

7

RRCLKES

I

Received Recovered Clock Edge Select Input:

Hardware Mode:

1. When RRCLKES = “0”, then RRPOS and RRNEG are updated on the falling

edge of RRCLK

2. When RRCLKES = “1”, then RRPOS and RRNEG are updated on the rising

edge of RRCLK

NOTE: This applies to all channels.

Host Mode

Connect this pin to GND when the 71D04 is configured in the Host Mode.

Internal 50 K Ohm pull-down resistor.

8

NC

No Connection

9

Reset

I

Reset Input. (Active-Low):

A high-low transition will re-center the internal FIFO, and will clear the Command

Registers (for Host Mode operation). Resetting this pin may corrupt data within

the device.

For normal operation, pull this pin to VDD.

Internal 50 K Ohm pull-up resistor.

10

DS3/E3_1

I

DS3/E3 Select Input - channel 1:

This pin along with the STS-1 mode select pin selects the operating mode. The

following table provides the configuration:

STS-1

DS3/E3

XRT71D04 Operating Mode

0

DS3

(44.736 MHz)

0

1

E3 (34.368 MHz)

1

0

STS-1 (51.84 MHz)

1

E3 (34.368 MHz)

Internal 50 K Ohm pull-down resistor.

11

VDD

****

Digital Power Supply = 5V±5% or 3.3V±5%

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT8000IP-F | IC WAN CLOCK E1/E1 DUAL 18PDIP |

| XRT8001IP-F | IC WAN CLOCK E1/E1 DUAL 18PDIP |

| XRT8010IL-F | IC CLK MULTIPLR LVDS 16QFN |

| XRT8020IL-F | IC CLK MULTIPLR LVDS 16QFN |

| XRT91L31IQ | IC TXRX SONET/SDH 8BIT 64QFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT71D04IVTR | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 4CH E3/DS3/STS1 JIT ATTEN DE-SYNCH RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT7250 | 制造商:EXAR 制造商全稱:EXAR 功能描述:DS3/E3 FRAMER IC |

| XRT7250ES-PCI | 功能描述:界面開(kāi)發(fā)工具 Evaluation Board for XRT7250 Series RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類(lèi)型:RS-485 工具用于評(píng)估:ADM3485E 接口類(lèi)型:RS-485 工作電源電壓:3.3 V |

| XRT7250IQ100 | 制造商:EXAR 制造商全稱:EXAR 功能描述:DS3/E3 FRAMER IC |

| XRT7288 | 制造商:EXAR 制造商全稱:EXAR 功能描述:CEPT1 Line Interface |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。