- 您現在的位置:買賣IC網 > PDF目錄16550 > XR16M781IB25-0C-EB (Exar Corporation)EVAL BOARD FOR XR16M781-C 25BGA PDF資料下載

參數資料

| 型號: | XR16M781IB25-0C-EB |

| 廠商: | Exar Corporation |

| 文件頁數: | 43/52頁 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR16M781-C 25BGA |

| 標準包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

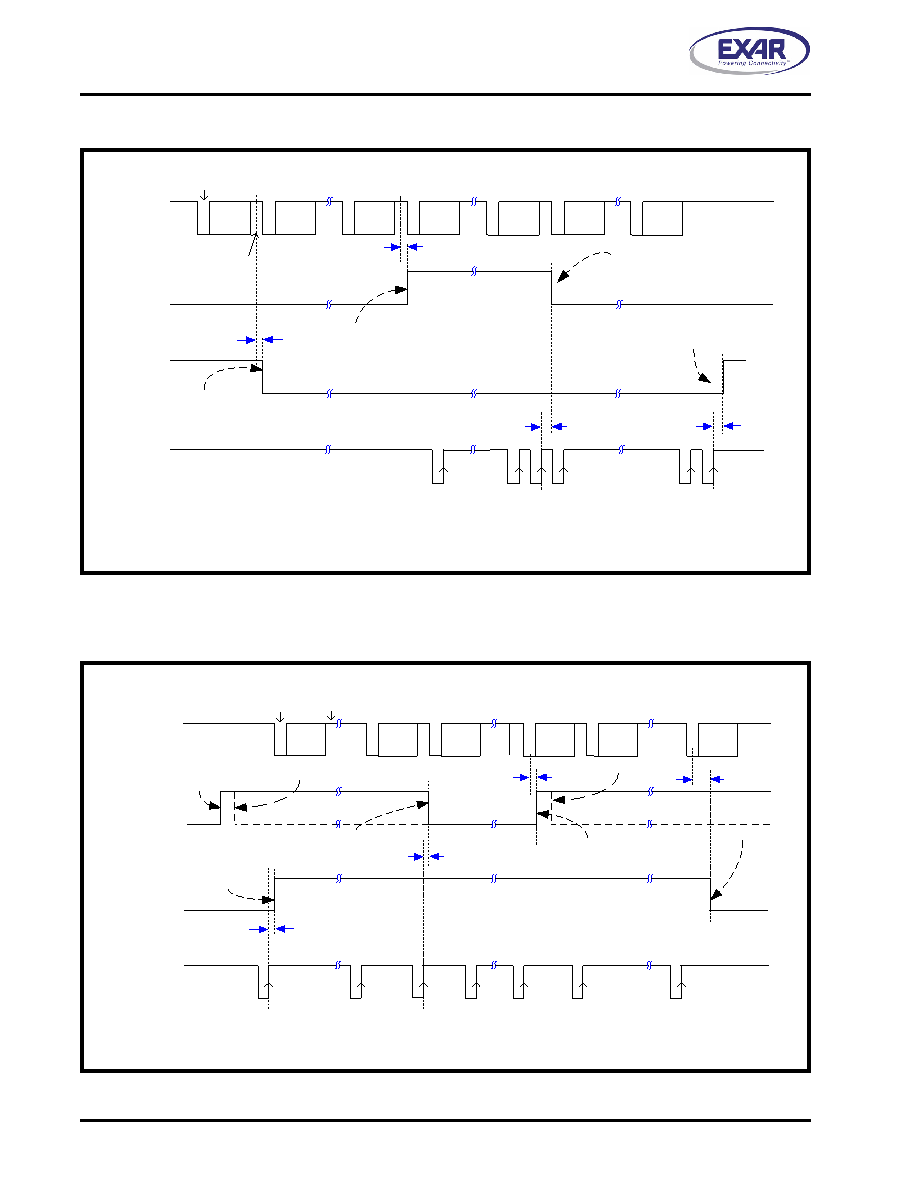

FIGURE 21. RECEIVE READY & INTERRUPT TIMING [FIFO MODE]

RX

RXRDY#

IOR#

INT

D0:D7

S

T

SSR

RXINTDMA#

RX FIFO fills up to RX

Trigger Level or RX Data

Timeout

RX FIFO drops

below RX

Trigger Level

FIFO

Empties

First Byte is

Received in

RX FIFO

D0:D7

S

D0:D7

T

D0:D7

S

D0:D7

S

T

D0:D7

S

T

D0:D7

S

T

Start

Bit

Stop

Bit

T

RR

T

RRI

T

SSI

(Reading data out

of RX FIFO)

FIGURE 22. TRANSMIT READY & INTERRUPT TIMING [FIFO MODE]

TX

TXRDY#

IOW#

INT*

TXDMA#

D0:D7

S

D0:D7

T

D0:D7

S

D0:D7

S

T

D0:D7

S

T

D0:D7

S

T

Start

Bit

Stop

Bit

T

WRI

(Unloading)

(Loading data

into FIFO)

Last Data Byte

Transmitted

TX FIFO fills up

to trigger level

TX FIFO drops

below trigger level

Data in

TX FIFO

Empty

T

WT

T

SRT

TX FIFO

Empty

T

S

T

SI

ISR is read

IER[1]

enabled

ISR is read

*INT is cleared when the ISR is read or when TX FIFO fills up to the trigger level.

XR16M781

48

1.62V TO 3.63V UART WITH 64-BYTE FIFO AND VLIO INTERFACE

REV. 1.0.1

相關PDF資料 |

PDF描述 |

|---|---|

| AYM06DRMD | CONN EDGECARD 12POS .156 WW |

| D-500-L455-1-612-120 | MICROCOUPLER 1 STUB SHIELD CABLE |

| ECE-T1HA183EA | CAP ALUM 18000UF 50V 20% SNAP |

| ECE-T1VA273EA | CAP ALUM 27000UF 35V 20% SNAP |

| AGM06DRMD | CONN EDGECARD 12POS .156 WW |

相關代理商/技術參數 |

參數描述 |

|---|---|

| XR16M781IB25-F | 功能描述:UART 接口集成電路 1.62-3.63V; 64-Byte FIFO & VLIO; UART RoHS:否 制造商:Texas Instruments 通道數量:2 數據速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16M781IL24 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V UART WITH 64-BYTE FIFO AND VLIO INTERFACE |

| XR16M781IL24-0C-EB | 功能描述:界面開發(fā)工具 Eval Board for XR16M781IL24 Series RoHS:否 制造商:Bourns 產品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| XR16M781IL24-F | 功能描述:UART 接口集成電路 1.62-3.63V; 64-Byte FIFO & VLIO; UART RoHS:否 制造商:Texas Instruments 通道數量:2 數據速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16M781IL32 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V UART WITH 64-BYTE FIFO AND VLIO INTERFACE |

發(fā)布緊急采購,3分鐘左右您將得到回復。