- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4291 > XC2S100E-6TQ144C (Xilinx Inc)IC FPGA 1.8V 600 CLB'S 144-TQFP PDF資料下載

參數(shù)資料

| 型號: | XC2S100E-6TQ144C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 60/108頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA 1.8V 600 CLB'S 144-TQFP |

| 產(chǎn)品變化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 標準包裝: | 60 |

| 系列: | Spartan®-IIE |

| LAB/CLB數(shù): | 600 |

| 邏輯元件/單元數(shù): | 2700 |

| RAM 位總計: | 40960 |

| 輸入/輸出數(shù): | 102 |

| 門數(shù): | 100000 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 144-LQFP |

| 供應(yīng)商設(shè)備封裝: | 144-TQFP(20x20) |

| 其它名稱: | 122-1206 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁當前第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁

DS077-4 (v3.0) August 9, 2013

55

Product Specification

Spartan-IIE FPGA Family: Pinout Tables

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

Spartan-IIE Package Pinouts

The Spartan-IIE family of FPGAs is available in five popu-

lar, low-cost packages, including plastic quad flat packs and

fine-pitch ball grid arrays. Family members have footprint

compatibility across devices provided in the same package,

with minor exceptions due to the smaller number of I/O in

smaller devices or due to LVDS/LVPECL pin pairing. The

Spartan-IIE family is not footprint compatible with any other

FPGA family. The following package-specific pinout tables

indicate function, pin, and bank information for all devices

available in that package. The pinouts follow the pad loca-

tions around the die, starting from pin 1 on the QFP pack-

ages.

Package Overview

Table 12 shows the five low-cost, space-saving production

package styles for the Spartan-IIE family.

Each package style is available in an environmentally

friendly lead-free (Pb-free) option. The Pb-free packages

include an extra ‘G’ in the package style name. For

example, the standard “TQ144” package becomes

“TQG144” when ordered as the Pb-free option. Leaded

(non-Pb-free) packages may be available for selected

devices, with the same pin-out and without the "G" in the

ordering code; contact Xilinx sales for more information.

The mechanical dimensions of the standard and Pb-free

packages are similar, as shown in the mechanical drawings

provided in Table 13.

For additional package information, see UG112: Device

Package User Guide.

Mechanical Drawings

Detailed mechanical drawings for each package type are

available from the Xilinx web site at the specified location in

Material Declaration Data Sheets (MDDS) are also

available on the Xilinx web site for each package.

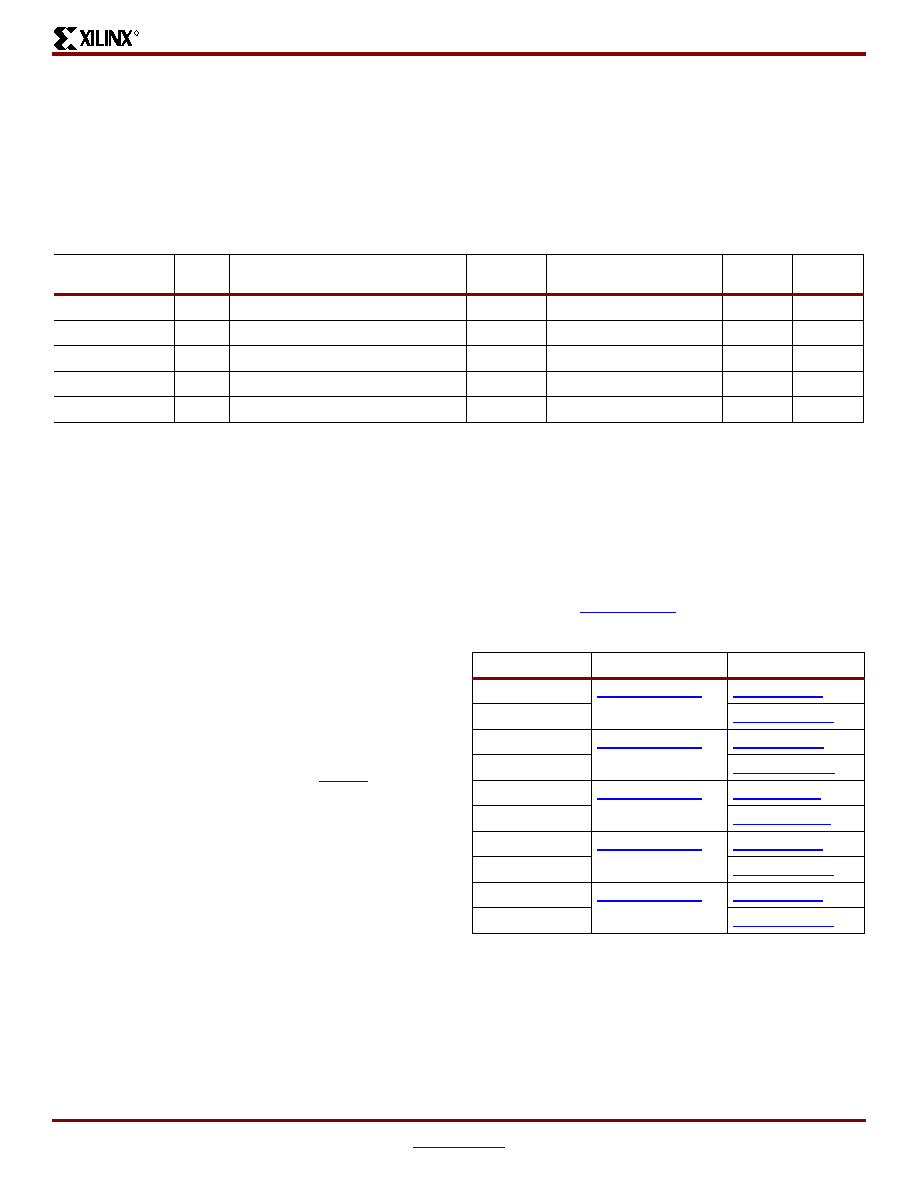

Table 12: Spartan-IIE Family Package Options

Package

Leads

Type

Maximum

I/O

Lead Pitch

(mm)

Footprint

Area (mm)

Height

(mm)

Mass(1)

(g)

TQ144 / TQG144

144

Thin Quad Flat Pack (TQFP)

102

0.5

22 x 22

1.60

1.4

PQ208 / PQG208

208

Plastic Quad Flat Pack (PQFP)

146

0.5

30.6 x 30.6

3.70

5.3

FT256 / FTG256

256

Fine-pitch Thin Ball Grid Array (FBGA)

182

1.0

17 x 17

1.55

1.0

FG456 / FGG456

456

Fine-pitch Ball Grid Array (FBGA)

329

1.0

23 x 23

2.60

2.2

FG676 / FGG676

676

Fine-pitch Ball Grid Array (FBGA)

514

1.0

27 x 27

2.60

3.1

Notes:

1.

Package mass is

±10%.

Table 13: Xilinx Package Documentation

Package

Drawing

MDDS

TQ144

TQG144

PQ208

PQG208

FT256

FTG256

FG456

FGG456

FG676

FGG676

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XA3S200-4PQG208I | IC FPGA SPARTAN-3 200K 208-PQFP |

| 24FC64FT-I/SN | IC EEPROM 64KBIT 1MHZ 8SOIC |

| XA2S50E-6TQ144Q | IC FPGA SPARTAN-IIE 144TQFP |

| RSA50DTBD-S664 | CONN EDGECARD 100PS R/A .125 SLD |

| XC3S200-4PQ208I | IC FPGA SPARTAN 3 208PQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S100E-6TQ144C0776 | 制造商:Xilinx 功能描述: |

| XC2S100E-6TQ144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE 1.8V FPGA Family |

| XC2S100E-6TQG144C | 功能描述:IC FPGA 1.8V 600 CLB'S 144-TQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-IIE 標準包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC2S100E-6TQG144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S100E7FG456C | 制造商:Xilinx 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。