- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359317 > V29C51002B (Mosel Vitelic, Corp.) High Speed 2 MEGA Bit 5 Volt CMOS Flash Memory(高速2M位5V CMOS閃速存儲(chǔ)器) PDF資料下載

參數(shù)資料

| 型號(hào): | V29C51002B |

| 廠商: | Mosel Vitelic, Corp. |

| 英文描述: | High Speed 2 MEGA Bit 5 Volt CMOS Flash Memory(高速2M位5V CMOS閃速存儲(chǔ)器) |

| 中文描述: | 高速2兆的5伏的CMOS快閃記憶體(200萬位高速5V的CMOS閃速存儲(chǔ)器) |

| 文件頁數(shù): | 1/16頁 |

| 文件大小: | 82K |

| 代理商: | V29C51002B |

MOSEL V ITELIC

1

V29C51002T/V29C51002B

2 MEGABIT (262,144 x 8 BIT)

5 VOLT CMOS FLASH MEMORY

PRELIMINARY

V29C51002T/V29C51002B Rev. 1.7 February 1999

Features

I

I

I

I

I

I

256Kx8-bit Organization

Address Access Time: 55, 70, 90, 120 ns

Single 5V

±

10% Power Supply

Sector Erase Mode Operation

16KB Boot Block (lockable)

512 bytes per Sector, 512 Sectors

– Sector-Erase Cycle Time: 10ms (Max)

– Byte-Write Cycle Time: 20

Minimum 10,000 Erase-Program Cycles

Low power dissipation

– Active Read Current: 20mA (Typ)

– Active Program Current: 30mA (Typ)

– Standby Current: 100

Hardware Data Protection

Low V

CC

Program Inhibit Below 3.5V

Self-timed write/erase operations with end-of-cy-

cle detection

– DATA Polling

– Toggle Bit

CMOS and TTL Interface

Available in two versions

– V29C51002T (Top Boot Block)

– V29C51002B (Bottom Boot Block)

Packages:

– 32-pin Plastic DIP

– 32-pin TSOP-I

– 32-pin PLCC

m

s (Max)

I

I

m

A (Max)

I

I

I

I

I

I

Description

The V29C51002T/V29C51002B is a high speed

262,144 x 8 bit CMOS flash memory. Writing or

erasing the device is done with a single 5 Volt

power supply. The device has separate chip enable

CE, write enable WE, and output enable OE

controls to eliminate bus contention.

The V29C51002T/V29C51002B offers a combi-

nation of: Boot Block with Sector Erase/Write

Mode. The end of write/erase cycle is detected by

DATA Polling of I/O

7

or by the Toggle Bit I/O

The V29C51002T/V29C51002B features a

sector erase operation which allows each sector to

be erased and reprogrammed without affecting

data stored in other sectors. The device also

supports full chip erase.

Boot block architecture enables the device to

boot from a protected sector located either at the

top (V29C51002T) or the bottom (V29C51002B).

All inputs and outputs are CMOS and TTL

compatible.

The V29C51002T/V29C51002B is ideal for

applications that require updatable code and data

storage.

6

.

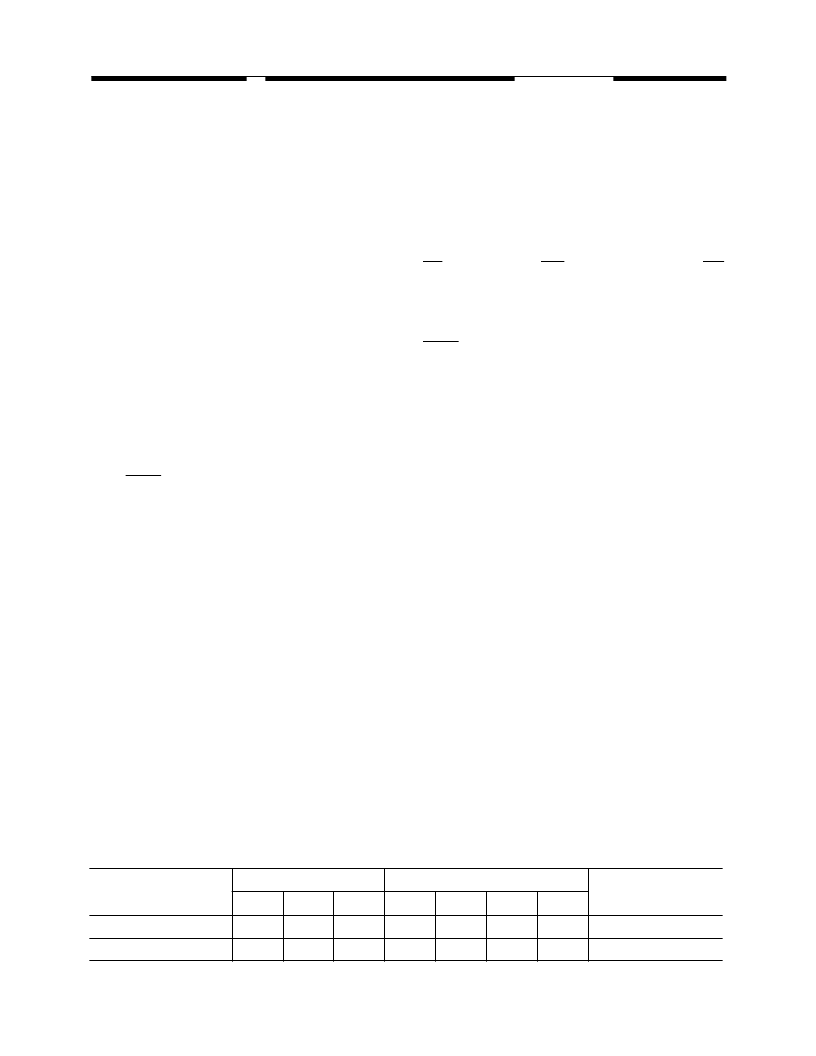

Device Usage Chart

Operating

Temperature

Range

Package Outline

Access Time (ns)

Temperature

Mark

P

T

J

55

70

90

120

0

°

C to 70

°

C

Blank

–40

°

C to +85

°

C

I

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V29C51004B-70J | x8 Flash EEPROM |

| V29C51004B-70T | x8 Flash EEPROM |

| V29C51004B-90J | x8 Flash EEPROM |

| V29C51004T-90T | x8 Flash EEPROM |

| V29C51004T-90J | x8 Flash EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| V29C51002B-55J | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:2 MEGABIT 262,144 x 8 BIT 5 VOLT CMOS FLASH MEMORY |

| V29C51002B-55P | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:2 MEGABIT 262,144 x 8 BIT 5 VOLT CMOS FLASH MEMORY |

| V29C51002B-55T | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:2 MEGABIT 262,144 x 8 BIT 5 VOLT CMOS FLASH MEMORY |

| V29C51002B-90J | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:2 MEGABIT 262,144 x 8 BIT 5 VOLT CMOS FLASH MEMORY |

| V29C51002B-90P | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:2 MEGABIT 262,144 x 8 BIT 5 VOLT CMOS FLASH MEMORY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。