- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384046 > UPD784915B (NEC Corp.) 16-BIT SINGLE-CHIP MICROCONTROLLERS PDF資料下載

參數(shù)資料

| 型號: | UPD784915B |

| 廠商: | NEC Corp. |

| 英文描述: | 16-BIT SINGLE-CHIP MICROCONTROLLERS |

| 中文描述: | 16位單晶片微控制器 |

| 文件頁數(shù): | 25/86頁 |

| 文件大小: | 384K |

| 代理商: | UPD784915B |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁

μ

PD784915B, 784916B

25

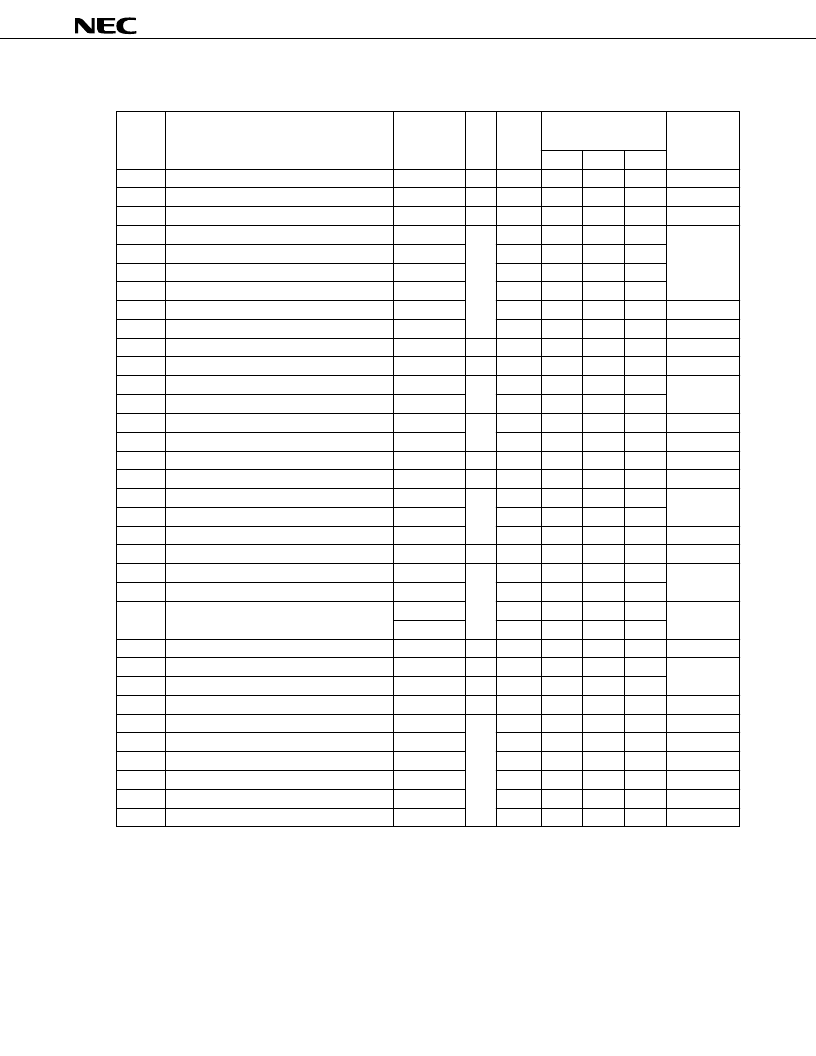

Table 3-2. Special Function Registers (2/4)

Bit

Bit Units for

After

Address

Special Function Register (SFR) Name

Symbol

R/W

Length

Manipulation

Releasing

1 bit

-

8 bits

-

16 bits

Reset

FF3CH

Timer register 3

TM3

R

16

√

-

Cleared to 0

FF3DH

Timer control register 4

TMC4

R/W

8

√

-

√

-

××

000000

FF3EH

Timer register 4

TM4

R

16

√

-

-

-

-

-

-

-

-

Cleared to 0

FF48H

Port 8 mode control register

PMC8

R/W

8

√

√

√

√

√

-

-

√

√

√

√

√

√

√

√

-

-

00H

FF4DH

Trigger source select register

TRGS0

8

FF4EH

Pull-up resistor option register L

PUOL

8

FF4FH

Pull-up resistor option register H

PUOH

8

FF50H

Input control register

ICR

8

10H

FF51H

Up/down counter count register

UDC

8

Undefined

FF52H

Event divider counter

EDV

R

8

Cleared to 0

FF53H

Capture mode register

CPTM

R/W

8

√

-

-

-

-

-

-

-

-

00H

FF54H

Timer register 5

TM5

R

16

√

√

-

-

-

-

Cleared to 0

FF56H

Timer 3 capture register 0

CPT30

16

FF58H

Timer 0 output mode register

TOM0

W

8

√

√

√

√

-

-

××

000000

FF59H

Timer 0 output control register

TOC0

TOM1

Note 1

8

00H

FF5AH

Timer 1 output mode register

R/W

8

80H

FF5BH

Timer 1 output control register

TOC1

W

8

00H

FF5CH

Timer 3 compare register 0

CR30

R/W

16

√

√

-

-

-

-

Cleared to 0

FF5EH

Timer 3 compare register 1

CR31

16

FF60H

Port 8 buffer register L

P8L

8

√

-

√

√

√

√

-

000

×

0

×

0

×

FF63H

Up/down counter compare register

UDCC

W

8

Undefined

FF65H

Trigger source select register 1

TRGS1

R/W

8

√

√

-

00H

FF66H

Port 6 mode control register

PMC6

8

FF68H

A/D converter mode register

ADM

16

√

-

-

0000H

ADML

Note 2

8

√

-

-

-

√

√

-

-

FF6AH

A/D conversion result register

ADCR

R

8

Undefined

FF6CH

Hardware watch counter 0

HW0

R/W

16

√

√

-

-

-

Not affected

FF6EH

Hardware watch counter 1

HW1

R

16

by reset

FF6FH

Watch mode register

WM

R/W

8

√

√

√

-

-

-

-

√

√

√

-

00

××

0

×

00

FF70H

PWM control register 0

PWMC0

R/W

8

05H

FF71H

PWM control register 1

PWMC1

8

15H

FF72H

PWM0 modulo register

PWM0

16

√

-

0000H

FF73H

PWM2 modulo register

PWM2

8

√

-

00H

FF74H

PWM1 modulo register

PWM1

16

√

-

0000H

FF75H

PWM3 modulo register

PWM3

8

√

00H

Notes 1.

When the timer 1 output mode register (TOM1) is read, the write sequence of the REC driver is read

(bits 0 and 1).

2.

ADML is the low-order 8 bits of the A/D converter mode register (ADM) and can be manipulated in 1-

or 8-bit units.

Remark

Cleared to 0: Counter is initialized to 0 within 16 clocks after the reset signal has been deasserted (the

contents before initialization are undefined).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD784915BGF | 16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD784916B | 16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD784916BGF | 16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD799 | 2048-BIT CCD IMAGE SENSOR |

| UPD8251A | PROGRAMMABLE COMMUNICATIONS INTERFACE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD784935AGF-113-3BA | 制造商:NEC Electronics Corporation 功能描述: |

| UPD784938AGF-188-3BA | 制造商:NEC Electronics Corporation 功能描述: |

| UPD789104AMC(A)-968-5A4-E2 | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD789104AMC-671-5A4-E1 | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD789104AMC-672-5A4-E1 | 制造商:Renesas Electronics Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。