- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383983 > UPD75004 (NEC Corp.) 4-BIT SINGLE-CHIP MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | UPD75004 |

| 廠商: | NEC Corp. |

| 英文描述: | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| 中文描述: | 4位單片機(jī) |

| 文件頁數(shù): | 39/66頁 |

| 文件大小: | 542K |

| 代理商: | UPD75004 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當(dāng)前第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

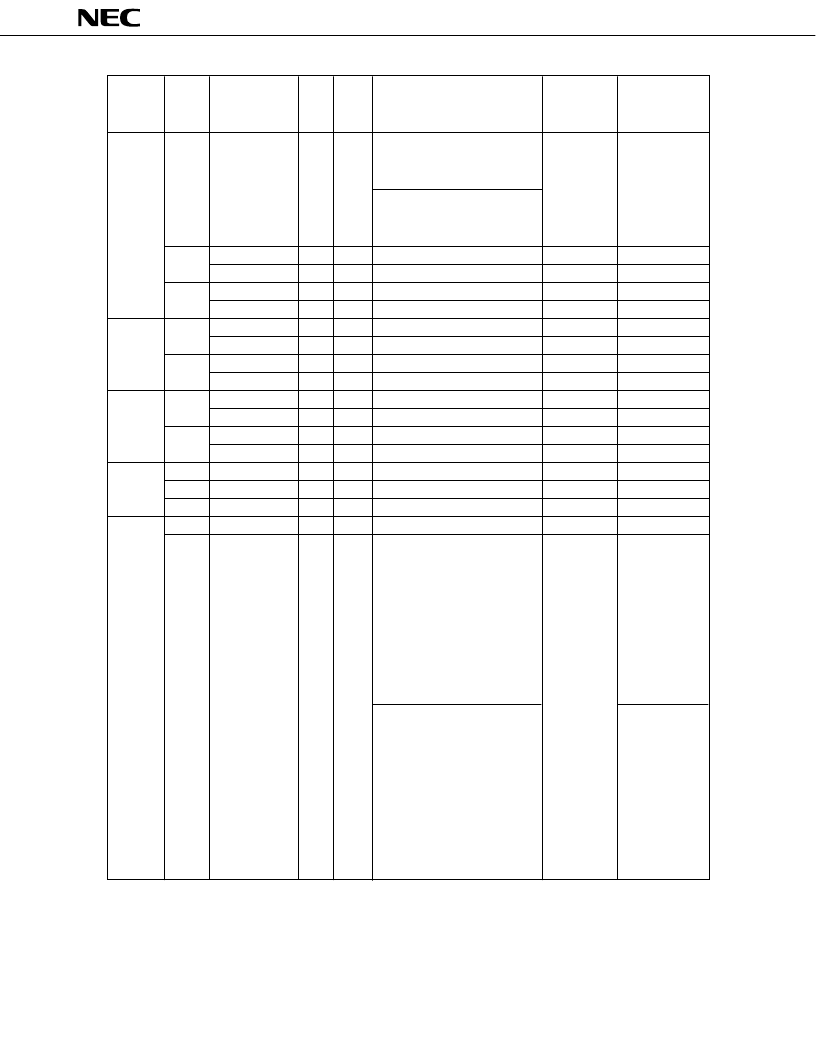

μ

PD75004, 75006, 75008

39

Ma-

chine

Cyc-

les

Ad-

dress-

ing

Area

Instruc-

tions

Mne-

monics

Operand

Bytes

Operation

Skip

Conditions

RETI

1

3

μ

PD75004

MBE, x, x, x

←

(SP+1)

PC

11-0

←

(SP)(SP+3)(SP+2)

PSW

←

(SP+4)(SP+5), SP

←

SP+6

μ

PD75006, 75008

MBE, x, x, PC

12

←

(SP+1)

PC

11-0

←

(SP)(SP+3)(SP+2)

PSW

←

(SP+4)(SP+5), SP

←

SP+6

(SP-1)(SP-2)

←

rp, SP

←

SP-2

(SP-1)

←

MBS, (SP-2)

←

0, SP

←

SP-2

rp

←

(SP+1)(SP), SP

←

SP+2

MBS

←

(SP+1), SP

←

SP+2

IME

←

1

IExxx

←

1

IME

←

0

IExxx

←

0

A

←

PORT

n

XA

←

PORT

n+1

,PORT

n

PORT

n

←

A

PORT

n+1

, PORT

n

←

XA

Set HALT Mode (PCC.2

←

1)

Set STOP Mode (PCC.3

←

1)

No Operation

MBS

←

n (n = 0, 1, 15)

μ

PD75004

Where TBR instruction,

11-0

←

(taddr)

3-0

+(taddr+1)

Where TCALL instruction,

(SP-4)(SP-1)(SP-2)

←

PC

11-0

(SP-3)

←

MBE, 0, 0, 0

PC

11-0

←

(taddr)

3-0

+(taddr+1)

SP

SP-4

.........................................................

PUSH

rp

BS

1

2

1

2

POP

rp

BS

1

2

2

2

1

2

2

2

Inter-

rupt

EI

IExxx

Control

DI

2

2

2

2

2

2

2

2

IExxx

A, PORTn

XA, PORTn

I/O

IN *

(n = 0-8)

(n = 4, 6)

OUT *

PORTn, A

PORTn, XA

2

2

2

2

2

2

2

2

(n = 2-8)

(n = 4, 6)

CPU

Control

HALT

STOP

NOP

SEL

GETI

1

2

1

1

2

3

Special

MBn

taddr

*10

Except for TBR and TCALL

instructions,

Instruction execution of

(taddr)(taddr+1)

Depends on

referenced

instruction

μ

PD75006, 75008

Where TBR instruction,

12-0

←

(taddr)

4-0

+(taddr+1)

.....PC

Where TCALL instruction,

(SP-4)(SP-1)(SP-2)

←

PC

11-0

(SP-3)

←

MBE, 0, 0, PC

12

PC

12-0

←

(taddr)

4-0

+(taddr+1)

SP

SP-4

.........................................................

Except for TBR and TCALL

instructions,

Instruction execution of

(taddr)(taddr+1)

Depends on

referenced

instruction

*: When executing the IN/OUT instruction, MBE = 0, or MBE = 1, and MBS = 15.

.....PC

.............................

.............................

.............................

.............................

Subrou-

tine/

Stack

Control

(Cont‘d)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD75004CU | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD75004GB | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD75006 | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD75006CU | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD75006GB | 4-BIT SINGLE-CHIP MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD750068GT-396 | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD7507C189 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD7508CU265 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD75208 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD753012AGC-P33-8BT-A | 制造商:Renesas Electronics Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。