- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98305 > TVP5146M2PFPR (TEXAS INSTRUMENTS INC) COLOR SIGNAL DECODER, PQFP80 PDF資料下載

參數(shù)資料

| 型號: | TVP5146M2PFPR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 顏色信號轉(zhuǎn)換 |

| 英文描述: | COLOR SIGNAL DECODER, PQFP80 |

| 封裝: | GREEN, PLASTIC, HTQFP-80 |

| 文件頁數(shù): | 24/107頁 |

| 文件大小: | 949K |

| 代理商: | TVP5146M2PFPR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁

x

Gain

Y

Limit

+

Offset

x

Gain

CbCr

Limit

SLES141G

– JULY 2005 – REVISED APRIL 2011

2.2.5

Component Video Processor

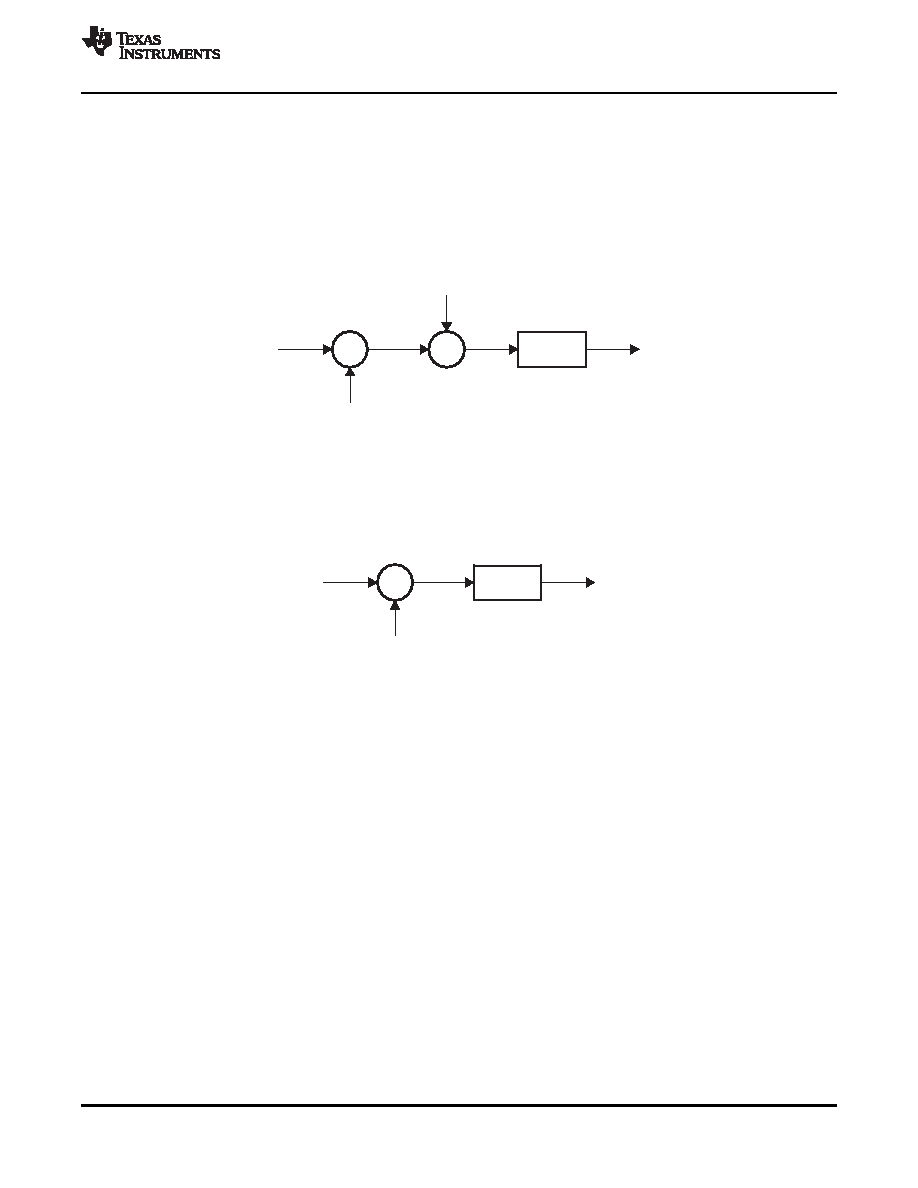

The component video processing block supports a user-selectable contrast, brightness, and saturation

adjustment in YCbCr output formats. For YCbCr output formats, gain and offset values are applied to the

luma data path to map the pixel values to the correct output range (for 10-bit Ymin = 64 and Ymax = 940),

and to provide a means of adjusting contrast and brightness. For Y, digital contrast (gain) and brightness

(offset) factors can vary from 0 to 255. The contrast control adjusts the amplitude range of the Y output

centered at the midpoint of the output code range. The limit block limits the output to the ITU-R BT.601

range (Ymin to Ymax) or an extended range, depending on a user setting.

Figure 2-10. Y Component Gain, Offset, Limit

For CbCr components, a saturation (gain) factor is applied to the CbCr inputs to map them to the CbCr

output code range and provide saturation control. Similarly, the limit block can limit CbCr outputs to a valid

range:

Cb,Crmin = 64 / Cb,Crmax = 960

Figure 2-11. CbCr Component Gain, Offset, Limit

2.2.6

Color Space Conversion

The formulas for RGB to YCbCr conversion are given as:

Y = 0.299

× R + 0.587 × G + 0.114 × B

Cb =

–0.172 × R – 0.339 × G + 0.511 × B + 512

Cr = 0.511

× R – 0.428 × G – 0.083 × B + 512

2.3

Clock Circuits

An internal line-locked PLL generates the system and pixel clocks. A 14.31818-MHz clock is required to

drive the PLL. This can be input to the TVP5146M2 decoder at the 1.8-V level on terminal 74 (XTAL1), or

a crystal of 14.31818-MHz fundamental resonant frequency can be connected across terminals 74 and 75

(XTAL2). If a parallel resonant circuit is used as shown in Figure 2-12, then the external capacitors must

have the following relationship:

CL1 = CL2 = 2CL CSTRAY

(1)

Where,

CSTRAY is the terminal capacitance with respect to ground

CL is the crystal load capacitance specified by the crystal manufacturer

Figure 2-12 shows the reference clock configurations. The TVP5146M2 decoder generates the DATACLK

signal used for clocking data.

Copyright

2005–2011, Texas Instruments Incorporated

Functional Description

23

Product Folder Link(s): TVP5146M2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TVP5146M2PFP | COLOR SIGNAL DECODER, PQFP80 |

| TVP5146M2PFPRG4 | COLOR SIGNAL DECODER, PQFP80 |

| TVP5146M2PFPG4 | COLOR SIGNAL DECODER, PQFP80 |

| TVP5146PFPRG4 | COLOR SIGNAL DECODER, PQFP80 |

| TVP5146PFP | COLOR SIGNAL DECODER, PQFP80 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TVP5146M2PFPRG4 | 制造商:Texas Instruments 功能描述: |

| TVP5146PFP | 功能描述:視頻 IC 10B High Qual S-Chip Dig Vid Decoder RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TVP5146PFP | 制造商:Texas Instruments 功能描述:IC VIDEO DECODER 10BIT 30MSPS HTQFP-80 制造商:Texas Instruments 功能描述:IC, VIDEO DECODER, 10BIT 30MSPS HTQFP-80 |

| TVP5146PFPG4 | 制造商:Texas Instruments 功能描述:10BIT VIDEO DECODER SMD HTQFP80 |

| TVP5146PFPR | 功能描述:視頻 IC NTSC/PAL/SECAM 4x10B Dig Vid Dec RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。